TSMC не успевает упаковывать достаточно чипов для ИИ-ускорителей NVIDIA — на устранение дефицита уйдёт 1,5 года

Экспертами не раз высказывалось мнение, что сейчас объёмы выпуска тех же ускорителей вычислений NVIDIA для систем искусственного интеллекта ограничиваются не возможностями TSMC по обработке кремниевых пластин, а её же способностью тестировать и упаковывать соответствующие чипы в нужных количествах. Руководство компании обещает устранить «узкие места» примерно за полтора года.

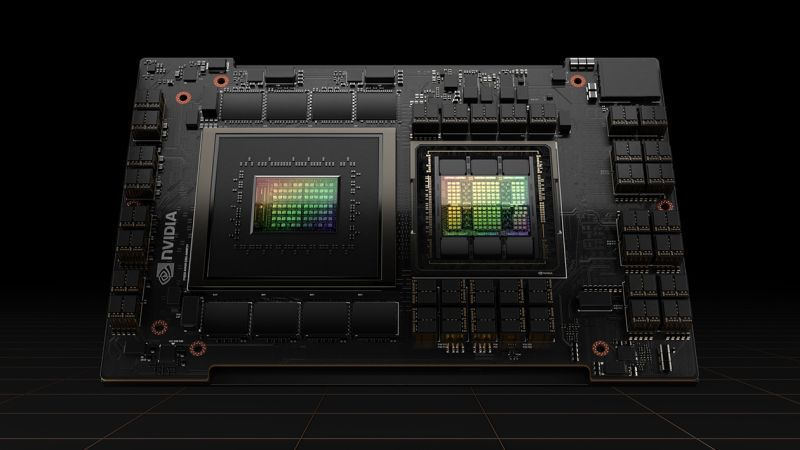

Источник изображения: NVIDIA

Об этом председатель совета директоров TSMC Марк Лю (Mark Liu), как отмечает Nikkei Asian Review, заявил на отраслевом мероприятии SEMICON, проходящем сейчас на Тайване. По его словам, имеющиеся ограничения носят временный характер и должны быть устранены к концу 2024 года. Марк Лю признался, что проблема кроется как раз в способности TSMC тестировать и упаковывать ограниченное количество чипов со сложной пространственной компоновкой, к которым относятся и ускорители NVIDIA A100 и H100.

Как поясняет представитель TSMC, в этом году спрос на упаковку чипов по методике CoWoS вырос внезапно, увеличившись в три раза. «Сейчас мы не можем удовлетворять 100 % потребностей клиентов, но стараемся покрывать хотя бы 80 %», — признался глава правления TSMC. Ситуация, по его мнению, носит временный характер, и по мере расширения мощностей по тестированию и упаковке чипов проблема будет устранена в течение полутора лет. На недавней квартальной отчётной конференции руководство TSMC пообещало к концу 2024 года удвоить профильные производственные мощности. Этому будет способствовать строительство нового комплекса по тестированию и упаковке чипов на Тайване, в которое TSMC вложит $2,9 млрд.

По словам Марка Лю, полупроводниковая отрасль должна смириться «со сменой парадигмы». Чтобы продолжать увеличивать количество транзисторов в чипах, производители должны активнее использовать сложные пространственные компоновки. Если сейчас флагманские ускорители могут объединять до 100 млрд транзисторов, по мнению руководства TSMC, то за ближайшие десять лет это количество увеличится в десять раз до более чем 1 трлн. Такой прогресс будет возможен благодаря объединению нескольких кристаллов в одной упаковке.

Кстати, компания Intel свои мощности по упаковке и тестированию чипов собирается к 2025 году увеличить в четыре раза, а также перепрофилировать под данный тип услуг свои предприятия, которые используют устаревающие литографические технологии.