Технологические планы Intel

Сегодня, когда размер мельчайших элементов логических микросхем - транзисторов - от поколения к поколению становится все меньше и меньше, а плотность их интеграции на кристалле полупроводникового устройства, согласно закону Мура, стремительно возрастает, разработчикам становится все труднее решать технологические проблемы, возникающие в силу действия естественных законов физики.

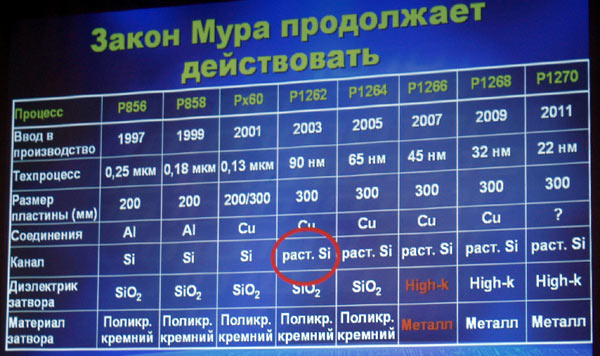

Roadmap Intel `2003-2011

Каждый переход на технологические нормы следующего поколения дарит разработчикам пышный букет проблем, связанных как с проектированием чипов, так и с последующим внедрением их в массовое производство.

Следующая табличка является ключевой для понимания технологических инноваций, запланированных на внедрение компанией Intel на ближайшие восемь лет:

Первое, что поражает - четкий двухгодичный цикл переходов на новые проектные нормы. Второй интересный фактор чуть ниже - это переход на новую канальную технологию (обведен красным кружочком), запланированный на нынешний год и новый материал диэлектрика затвора и самого затвора (помечены красным), запланированный на 2007-й год.

Вот на этих технологиях и остановимся подробно.

I. Strained silicon technology (растянутый кремний)

Впервые технология "растянутого кремния" (strained silicon technology) будет реализована при производстве микросхем с проектной нормой 0,09 микрон - тот самый Prescott, выход которого ожидается со дня на день и в Pentium M следующего поколения, известном как Dothan.

Идея технологии "растянутого кремния" предельно проста. В процессе миниатюризации транзисторов и уменьшения площади их сечения возрастает сопротивление электрическому току, который проходит через транзистор. В результате транзистор "срабатывает" гораздо медленнее, чем хотелось бы, а тепловыделение, наоборот, только увеличивается. Специалисты корпорации Intel решили "растянуть" кристаллическую решетку в транзисторе, чтобы увеличить расстояние между атомами и облегчить протекание тока.

При этом инженеры подразделения Logic Technology Development Division корпорации Intel разработали два независимых способа "растяжения" кремния для разных типов транзисторов. Напомним, что существует два типа CMOS-транзисторов (CMOS, complimentary metal oxide semiconductor - полупроводниковая технология, применяемая при изготовлении всех логических микросхем, включая микропроцессоры и чипсеты): N-типа, обладающие электронной проводимостью, и P-типа, характеризующиеся проводимостью дырочной. Так вот, в NMOS-устройствах поверх транзистора в направлении движения электрического тока наносится слой нитрида кремния (Si3N4), в результате чего кремниевая кристаллическая решетка и "растягивается".

Транзисторы по технологии растянутого кремния

В PMOS-устройствах "растяжение" достигается за счет нанесения слоя SiGe в зоне образования переносчиков тока - здесь решетка "сжимается" в направлении движения электрического тока, и потому "дырочный" ток течет свободнее. В обоих случаях прохождение тока значительно облегчается: в первом случае - на 10%, во втором - на 25%. Сочетание же обеих технологий дает 20-30-процентное ускорение тока.

Технология уже внедрена на фабриках Intel D1C в Хиллсборо (шт. Орегон) и 11Х в Рио-Ранчо (шт. Нью-Мексико). Третьей фабрикой по производству 90-нм продукции Intel станет Fab24 в Лейкслипе (Ирландия), которая вступит в строй в первой половине 2004 года.

II. "high-k"

Главными барьерами на пути миниатюризации транзисторов являются выделение тепла при работе транзистора и утечка электрического тока в том же процессе. Чем меньше транзистор, тем выше тепловыделение и больше ток утечки.

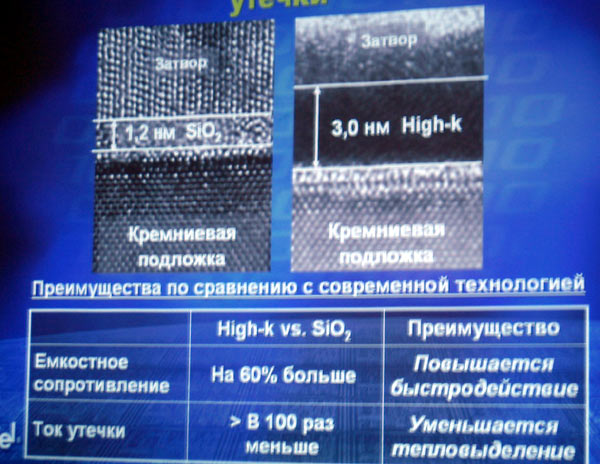

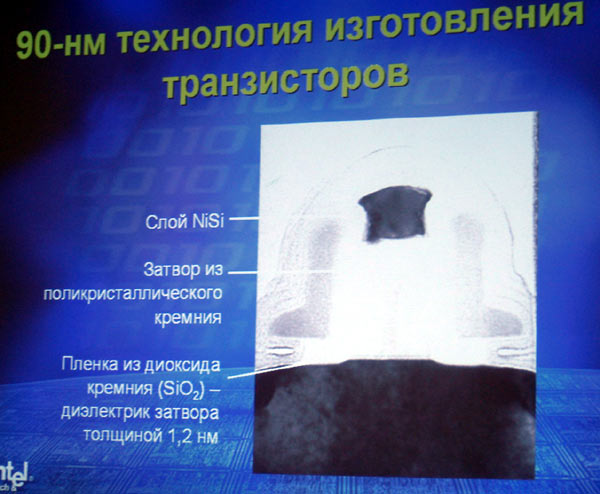

Все полевые транзисторы содержат специальный изолирующий слой - тонкую диэлектрическую пленку под затвором, т.е. электродом, управляющим "включением" и "выключением" транзистора. Свойства диэлектрика затвора оказывают решающее влияние на работу транзистора. Последние 30 лет в качестве основного материала для диэлектрика затвора использовался диоксид кремния (SiO2), что было обусловлено его технологичностью и возможностью систематического улучшения характеристик транзисторов по мере уменьшения их размеров. На сегодняшний день в транзисторах, производимых корпорацией Intel, толщина слоя диэлектрика затвора из диоксида кремния составляет всего 1,2 нанометра - то есть, сопоставима с пятью атомарными слоями. Фактически, это уже близко к пределу для данного материала, поскольку в результате дальнейшего уменьшения самого транзистора и, как следствие, утоньшения слоя диоксида кремния ток утечки через диэлектрик затвора значительно возрастет, что приведет к существенным потерям тока и избыточному тепловыделению. По оценкам экспертов корпорации Intel, в современных чипах уже почти 40% энергии теряется из-за утечек.

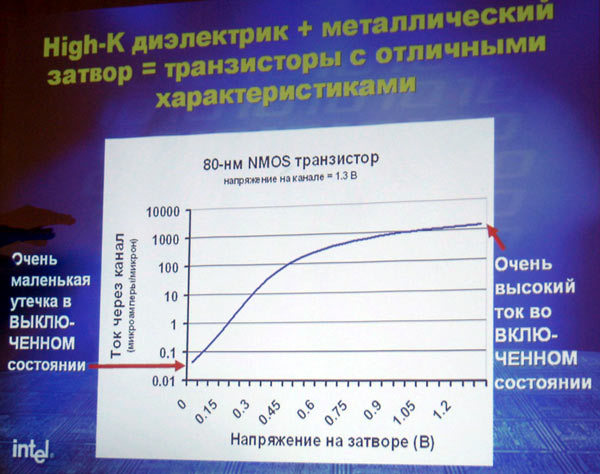

Intel предлагает сразу два технологических решения, которые позволяют преодолеть вышеупомянутые сложности. Для решения все возрастающих проблем тепловыделения и тока утечки корпорация Intel планирует заменить используемый в настоящее время в качестве диэлектрика затвора тонкий слой диоксида кремния более толстым слоем совершенно нового диэлектрика с высоким диэлектрическим коэффициентом "к" (так называемым "high-k" диэлектриком), что позволит существенно - примерно в 100 раз! - снизить токи утечки. Вторая часть решения заключается в разработке нового материала (сплава металлов) для затвора, поскольку новый "high-k" диэлектрик плохо совместим с прежним материалом затвора - поликристаллическим кремнием.

Специалисты Intel убеждены, что новые материалы можно будет интегрировать в экономически эффективный, массовый производственный процесс. Транзисторы на основе новых материалов, обладающие рекордными параметрами производительности, рассматриваются в качестве базового варианта для изготовления будущих процессоров Intel в рамках производственного процесса с проектной нормой 45 нанометров (техпроцесс под кодовым номером 1266 на основе 300-мм подложек, медных соединений, технологии "растянутого кремния", а также нового затвора и диэлектрика затвора будет запущен в массовое производство уже в 2007 году).

Подробности о материалах, используемых в диэлектрике "high-k" и новом "металическом" затворе пока не разглашаются.

III. 90-нм технологический процесс

Однако, вернемся к 90-нм технологическому процессу (кодовое наименование Р1262). Кроме новой технологии "растянутого кремния", в нем используются и другие не менее интересные разработки: транзисторы с низким энергопотреблением, 7 слоев высокоскоростных и более плотных медных соединений с новым диэлектрическим материалом с низким диэлектрическим коэффициентом "к" (материал уменьшает величину паразитной емкости, которая возникает между медными соединительными проводами в чипе, повышает скорость передачи сигналов внутри чипа и снижает энергопотребление).

Впервые все эти разработки объединены в едином производственном процессе. А реальное их воплощение через месяц-другой будет спокойно лежать на прилавках.

По материалам презентации Intel "Второе дыхание закона Мура" (Frank E. Spindler, Moscow, 17.11.2003)

Френк Спиндлер (Frank E. Spindler) - вице-президент Intel Corporate Technology Group и директор программ Industry Technology Program. Он является одним из руководителем подразделения Intel, которое занимается разработкой и осуществлением различных технологических программ, включая IDF, а так же координирует деятельность группы по стандартам, международные программы и технологический маркетинг.

Дополнительные материалы:Оригинал материала: http://3dnews.kz/172008

© 1997-2025 3DNews | Daily Digital Digest | Лицензия Минпечати Эл ФС 77-22224

При цитировании документа ссылка на сайт с указанием автора обязательна. Полное заимствование документа является нарушением российского и международного законодательства и возможно только с согласия редакции 3DNews.

|