|

Опрос

|

реклама

Быстрый переход

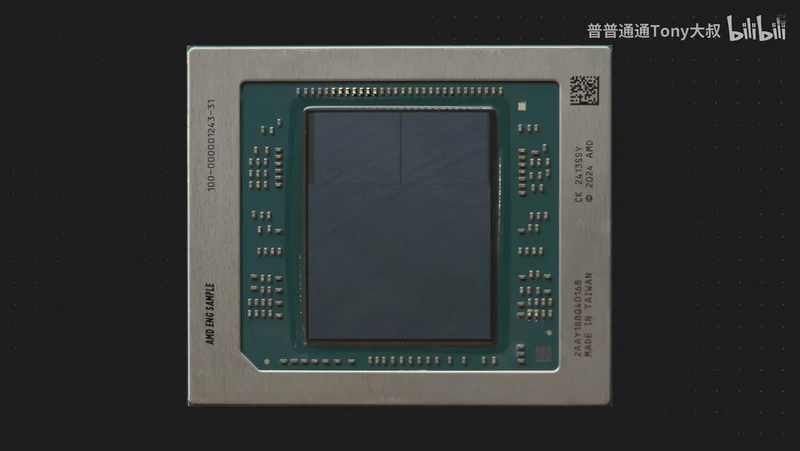

Кристаллы процессоров AMD Strix Halo с огромным iGPU показались на детальных фото

19.02.2025 [13:10],

Николай Хижняк

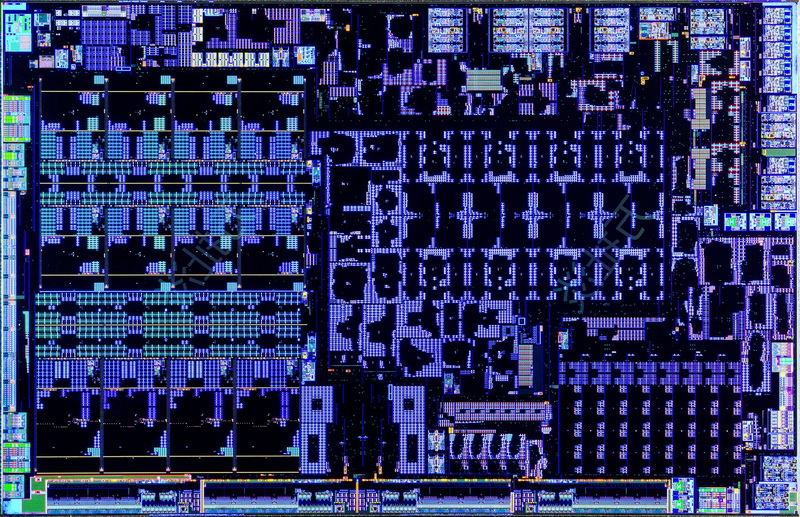

Энтузиасты опубликовали подробное изображение 4-нм кристалла нового мобильного процессора AMD Strix Halo (Ryzen AI 300 Max), на котором отчётливо видны все компоненты чипа. Вместе с изображением было представлено детальное описание того, какие именно элементы содержатся в процессоре.

Источник изображений: BiliBili В новых процессорах Strix Halo используется чиплетная конструкция. Они состоят из двух блоков CCD (каждый площадью 67,07 мм²) с вычислительными ядрами Zen 5, а также огромного чиплета ввода-вывода (I/O Die) площадью 307,58 мм², в котором размещаются встроенная графика с 40 вычислительными блоками на архитектуре RDNA 3.5 и мощный ИИ-ускоритель (NPU) XDNA2 с производительностью 50 TOPS (триллионов операций в секунду). Общая площадь процессора составляет 441,72 мм². Подсистема памяти Strix Halo поддерживает 256-битный интерфейс (восемь 32-битных контроллеров) для LPDDR5 и обеспечивает пропускную способность до 256 Гбайт/с. Процессор имеет 32 Мбайт общего кеша LLC (Last Level Cache) и по 8 Мбайт кеш-памяти L2 на каждый блок CCD. Снимки чипа также демонстрируют некоторые конструктивные особенности и оптимизацию для мобильной платформы. В частности, AMD сократила расстояние между блоками CCD у Strix Halo на 2 мм по сравнению с CCD своих настольных процессоров. Также у чипа можно отметить наличие структур сквозных кремниевых соединений (TSV), предполагающих совместимость с технологией 3D V-Cache, хотя сама AMD официально не подтверждала планы по реализации этой технологии в данных процессорах. Помимо 40 блоков встроенной графики и нейропроцессора XDNA2 NPU, чиплет I/O Die обеспечивает поддержку шестнадцати линий PCIe 4.0, оснащён контроллерами USB4, USB 3.2, USB и USB 2.0, а также двумя Media Engine с полной поддержкой H.264, H.265 и AV1 и одним Display Engine. Последний отвечает за кодирование выходного кадра iGPU в различные форматы разъёмов (такие как DisplayPort, eDP, HDMI). Одним из первых мобильных устройств с процессорами Strix Halo станет мощный игровой планшет Asus ROG Flow Z13, который поступит в продажу 25 февраля. Предзаказы на устройство уже принимаются. Новинка успела побывать в руках обозревателей, которые весьма высоко оценили вычислительные и графические возможности новых процессоров Ryzen AI 300 Max. Asus показала детальные снимки каждого кристалла Intel Core Ultra 200S

22.10.2024 [15:32],

Николай Хижняк

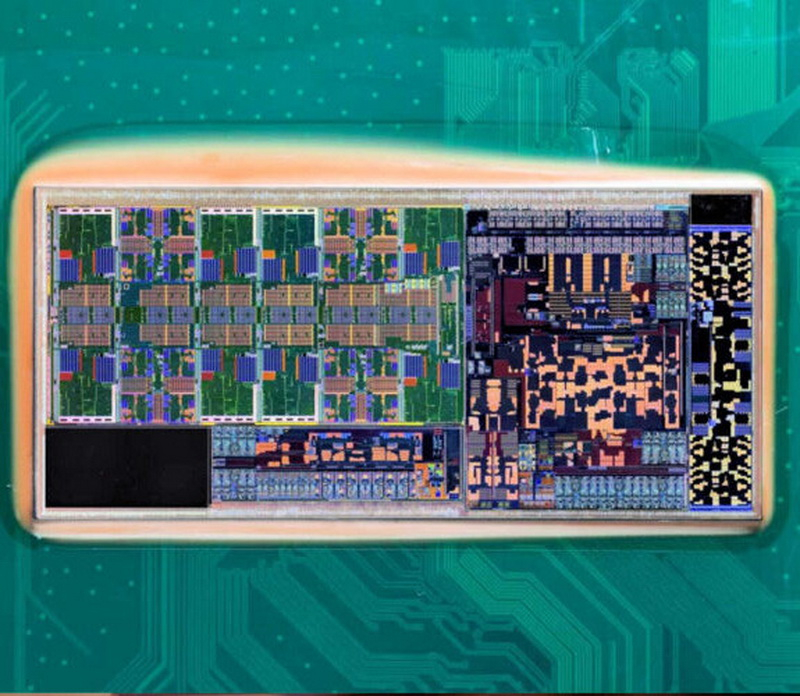

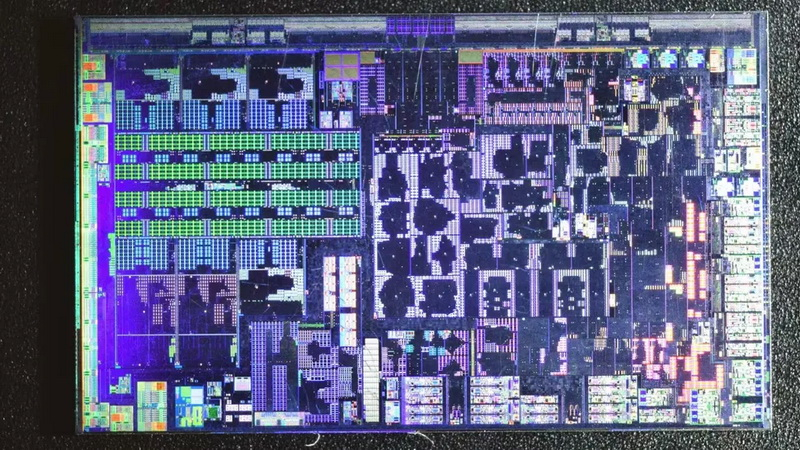

Настольные процессоры нового поколения Intel Core Ultra 200S поступят в продажу 24 октября. По этому случаю китайский офис компании Asus решил опубликовать видео, в котором рассказал о материнских платах на чипсете Intel Z890, предназначенных для этих чипов. В этом ролике компания также в деталях рассказала об особенностях архитектуры самих процессоров Intel.

Источник изображений: Asus Asus не только сняла теплораспределительную крышку с одного из процессоров серии Core Ultra 200S, но также убрала верхний кремниевый слой с его четырёх чиплетов, чтобы рассказать об их особенностях. Процессоры Core Ultra 200S состоят из четырёх логических компонентов (плиток или чиплетов), объединённых на подложке Foveros: вычислительного чиплета с ядрами CPU, кристалла SoC, блока встроенной графики (iGPU), а также кристалла интерфейсов ввода-вывода (I/O Die). У Core Ultra 200S также имеются два чиплета-пустышки, которые на предоставленных Asus изображениях выглядят как пустоты (чёрные области). Вычислительный чиплет с ядрами производится на базе самого передового технологического процесса среди четырёх кристаллов в составе Core Ultra 200S — TSMC N3B класса 3 нм. В отличие от предыдущих поколений процессоров Raptor Lake-S и Alder Lake-S у новых Arrow Lake-S производительные P-ядра и энергоэффективные E-ядра не сгруппированы друг с другом. Большие и малые ядра процессоров Core Ultra 200S расположены поочерёдно: за рядом P-ядер следует кластер E-ядер, за которым следует два ряда P-ядер, а после них ещё один кластер E-ядер перед последним рядом P-ядер. В конечном итоге получается конфигурация из восьми P-ядер и 16 E-ядер. Такая схема расположения ядер снижает концентрацию тепла при загрузке P-ядер (например, во время игр) и гарантирует, что каждый кластер E-ядер находится всего в одном шаге от кольцевой шины и от P-ядра, что должно улучшить задержки миграции потоков. Сама кольцевая шина, а также 36 Мбайт кеш-памяти L3, совместно используемой P- и E-ядрами, находятся в центральной области чиплета. Чиплет SoC процессоров Core Ultra 200S производится по 6-нм техпроцессу TSMC N6 с применением литографии в глубоком ультрафиолете. По обоим концам кристалла расположены схемы PHY, отвечающие за работу различных интерфейсов ввода-вывода. На одной стороне чиплета расположена схема PHY для DDR5, на другой — для PCI Express. Чиплет SoC обеспечивает поддержку 16 линий PCIe 5.0 для разъёмов PCIe x16 на материнской плате. В составе SoC присутствует блок NPU (ИИ-ускоритель), который, судя по всему, позаимствован у SoC процессоров Meteor Lake. Его пиковая ИИ-производительность составляет 13 TOPS (триллионов операций в секунду). Также в составе SoC присутствует сопроцессоры безопасности платформы, а также некоторые элементы iGPU, включая контроллер дисплея (Display Engine), ускорители мультимедиа и т.д. Помимо шины чипсета DMI 4.0 x8 чиплет I/O (тоже 6-нм техпроцесс TSMC N6) обеспечивает работу четырёх линий PCIe 5.0 и четырёх PCIe 4.0 для NVMe-накопителей. Линии PCIe 4.0 из I/O-чиплета можно переконфигурировать для поддержки интерфейсов Thunderbolt 4 или USB4. Чиплет встроенной графики (iGPU) процессоров Core Ultra 200S производится с применением 5-нм техпроцесса TSMC N5. С использованием этого же техпроцесса (одной из его версий) выпускаются графические процессоры актуальных видеокарт Nvidia с архитектурой Ada Lovelace и AMD с RDNA 3. В составе этого чиплета присутствуют четыре графических ядра Xe, а также различные элементы для рендеринга изображения. Опубликованы детализированные изображения кристаллов Ryzen 9000

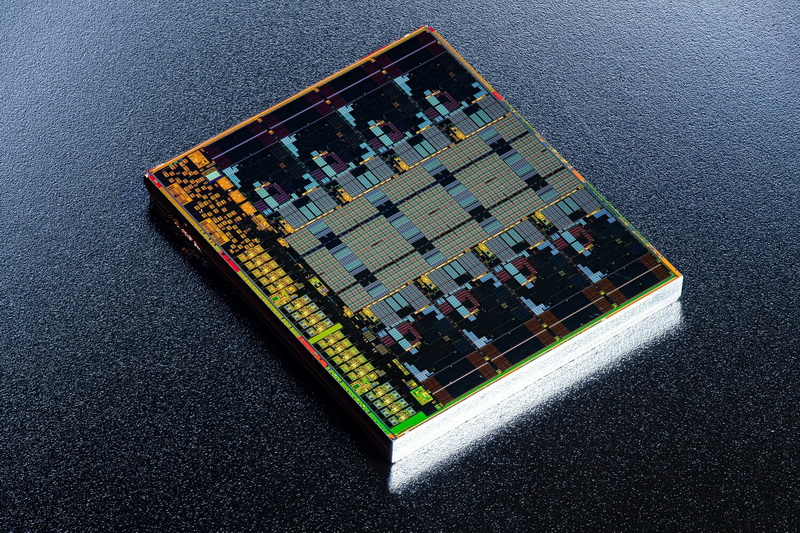

07.10.2024 [16:52],

Николай Хижняк

Технические энтузиасты провели полную разборку одного из процессоров серии Ryzen 9000 (Granite Ridge) и поделились высокодетализированными изображениями кристаллов CCD (с ядрами Zen 5) и cIOD (ввода-вывода) новых процессоров.

Источник изображений: X / @FritzchensFritz Упаковка новых чипов похожа на упаковку предшественников Ryzen 7000 (Raphael). В зависимости от модели чип может содержать один или два восьмиядерных чиплетов CCD, а также один кристалл ввода-вывода (cIOD), располагающийся в центральной части процессорной платы. Кристалл cIOD новые Ryzen 9000 позаимствовали у предшественников. Таким образом AMD удалось снизить затраты на разработку новых чипов. Кристаллы CCD с ядрами Zen 5 производятся с применением 4-нм техпроцесса TSMC N4P. Ядра в составе CCD процессоров Granite Ridge расположены ближе друг к другу, чем в CCD процессоров Raphael на Zen 4. Каждый CCD Granite Ridge содержит по 8 полноразмерных ядер Zen 5, в составе каждого из которых имеется по 1 Мбайт кеш-памяти L2. В центральной части CCD расположены 32 Мбайт кеш-памяти L3, распределяющиеся между ядрами. Другими компонентом CCD является контроллер управления SMU (System Management Unit) и физическая реализация шины Infinity Fabric over Package (IFoP), которая нужна для соединения чиплетов CCD и cIOD. Каждое ядро Zen 5 по размерам больше, чем Zen 4 (производится с применением техпроцесса TSMC N5), ввиду использования блока FPU с врождённой поддержкой 512-битных данных для AVX-512. Векторный движок (Vector Engine) вынесен к самому краю ядра. Это имеет смысл, поскольку FPU является самым горячим компонентом ядра CPU. На другом краю ядра, ближе к общему L3-кешу находятся два блока кеш-памяти L2 по 512 Кбайт. AMD удвоила пропускную способность и ассоциативность этой кеш-памяти по сравнению с Zen 4. В центральной области Zen 5 находятся 32 Кбайт кеш-памяти L1I, 48 Кбайт кеш-памяти L1D, целочисленные исполнительные устройства (Integer Execution Engine), а также входная часть конвейера процессора с блоком выборки и декодирования инструкций (Instruction Fetch & Decode), блоком прогнозирования ветвлений (Branch Prediction Unit), кешем микроопераций и планировщиком (Scheduler). Кеш L3 в центральной части кристалла CCD объёмом 32 Мбайт имеет ряды TSV (сквозные кремниевые переходные отверстия), которые служат заделом для потенциальной «склейки» с дополнительным кристаллом кеша 3D V-Cache. Кристалл 3D V-Cache объёмом 64 Мбайт с помощью этих TSV может быть подключен напрямую к внутренней кольцевой шине CCD. Кристалл cIOD в составе новых процессоров производится с применением 6-нм техпроцесса TSMC N6. Примерно 1/3 его площади занимает встроенный блок iGPU и его смежные компоненты, такие как мультимедийный движок и механизм отображения. iGPU, как и ранее, основан на графической архитектуре RDNA 2 и оснащён всего одной группой процессоров рабочих групп (WGP) с двумя исполнительными блоками (CU) или 128 потоковыми процессорами. Другим ключевым компонентом cIOD является интерфейс PCIe Gen 5 с поддержкой 28 линий, два интерфейса IFoP для межкристального соединения с ядерными блоками CCD, довольно большой SoC I/O с поддержкой USB 3.x и других типов интерфейсов, а также одна из важнейших частей процессора — контроллер памяти DDR5 с двуканальным (с четырьмя подканалами) интерфейсом. Снимок кристалла Qualcomm Snapdragon X Elite раскрыл истинные размеры ядер Oryon

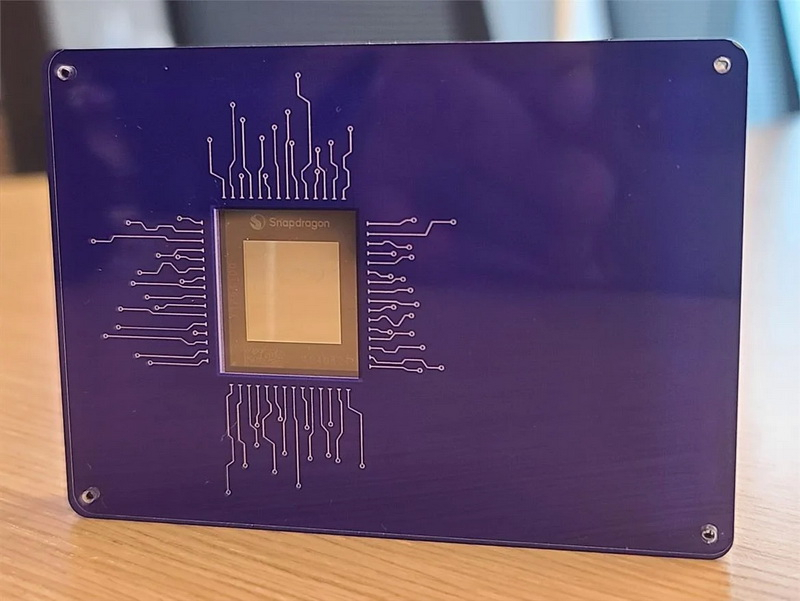

01.10.2024 [22:41],

Николай Хижняк

В китайской социальной сети Baidu энтузиасты поделились изображением кристалла ПК-процессора Qualcomm Snapdragon X Elite. Благодаря этому появилось возможность узнать из чего состоит этот чип. Анализ дает представление об архитектуре указанной SoC (системе-на-чипе) и выделяет несколько её ключевых особенностей, включая большие ядра CPU, графический процессор и сложную систему кеширования.

Источник изображения: HotHardware Согласно имеющейся информации, площадь кристалла Snapdragon X Elite составляет 169,6 мм2. Для его выпуска используется 4-нм техпроцесс N4P компании TSMC. Примечательным на снимке кристалла является значительный размер ядер Oryon (Phoenix), каждое из которых, как сообщается, имеет размер около 2,55 мм2. Эти ядра значительно больше типичных ядер процессоров Arm, что логично, учитывая их изначальное предназначение для центров обработки данных. SoC имеет в общей сложности 12 ядер, работающих в конфигурации 8+4. В составе кристалла также присутствует блок GPU Adreno X1, занимающий до 24,3 мм2 площади кристалла, что составляет почти половину от размера площади процессорных ядер и кеша CPU. Несмотря на свои компактные размеры, этот GPU, со слов Qualcomm, обладает чистой производительностью на уровне 4,6 Тфлопс. Блок ИИ-ускорителя (NPU) с производительностью 45 TOPS (триллионов операций в секунду) на снимке отчётливо не виден. Другой интересной особенностью кристалла Snapdragon X Elite является его сложная система кеш-памяти. Каждый из трёх четырёхъядерных кластеров L2-кеша процессора занимает площадь 16,1 мм2 и имеет объём 12 Мбайт. Но в общей сложности процессор имеет 54 Мбайт кеш-памяти, распределённых по кристаллу. Предоставленный анализ также сравнивает кристалл Snapdragon X Elite с SoC Apple M4. Однако стоит отметить, что это не совсем корректное сравнение, поскольку для производства чипа Apple используется техпроцесс N3E класса 3 нм. Изображение кристалла M4 от Apple с аннотациями можно посмотреть выше. Кристалл мобильных процессоров AMD Strix Point с ядрами Zen 5 и Zen 5c показался на подробном изображении

30.07.2024 [21:42],

Николай Хижняк

Энтузиасты опубликовали подробное изображение 4-нм кристалла нового мобильного процессора AMD Strix Point (Ryzen AI 300), на котором отчётливо видны все компоненты чипа. Вместе с изображением было представлено подробное описание того, какие компоненты содержатся в чипе.

Источник изображения: BiliBili Новый Strix Point значительно больше кристалла Phoenix — его размеры составляют 12,06 × 18,71 мм против 9,06 × 15,01 мм у чипа прошлого поколения. Увеличение площади в основном связано с тем, что Strix Point получил более крупные блоки CPU, iGPU и NPU. Кроме того, AMD перевела кристалл нового чипа с техпроцесса TSMC N4 (Phoenix и его наследник Hawk Point) на усовершенствованный техпроцесс TSMC N4P. Новый процессор получил 12 вычислительных ядер, разделённых на два блока CCX, в одном из которых содержатся четыре ядра Zen 5 и 16 Мбайт кеш-памяти L3, а во втором — восемь энергоэффективных ядер Zen 5c и выделенные для них 8 Мбайт кеш-памяти L3. Блоки CCX соединяются с остальными компонентами процессора шиной Infinity Fabric. Весьма крупный блок iGPU занимает центральную часть кристалла. Он основан на графической архитектуре RDNA 3.5 и содержит восемь процессоров рабочих групп (WGP) или 16 исполнительных блоков (CU), в составе которых присутствуют 1024 потоковых процессора. Другие ключевые компоненты iGPU включают четыре блока рендеринга с 16 ROP и управляющую логику. Встроенная графика Strix Point имеет собственные 2 Мбайт кеш-памяти L2. Рядом с iGPU, в правой части кристалла Strix Point находятся его родственные компоненты Media Engine и Display Engine. Первый обеспечивает аппаратное ускорение для кодирования и декодирования h.264, h.265 и AV1, а также нескольких устаревших видеоформатов. Display Engine отвечает за кодирование выходного кадра iGPU в различные форматы разъёмов (такие как DisplayPort, eDP, HDMI), включая аппаратно-ускоренное сжатие потока (DSC). Схемы Display PHY отвечают за физический уровень подключения iGPU к видеоразъёмам. Блок NPU является третьим ключевым логическим компонентом Strix Point. В новых процессорах AMD используется второе поколение NPU, чьи физические размеры стали заметно больше, чем у Phoenix. Новый NPU основан на продвинутой архитектуре XDNA 2 и содержит 32 плитки ИИ-движка, которые взаимодействуют с собственной высокоскоростной локальной памятью и управляющей логикой, которая в свою очередь подключена к шине Infinity Fabric. Этот NPU разработан в соответствии с требованиями Microsoft для ПК экосистемы Copilot Plus PC и обладает производительностью 50 TOPS (триллионов операций в секунду). Контроллер памяти в Strix Point поддерживает двухканальную (160-битную) ОЗУ DDR5-5600 и 128-битную LPDDR5 со скоростью до 7500 МТ/с. Контроллер имеет неуказанный размер кэша SRAM, который, как отмечается, также был замечен в кристаллах Phoenix 2 и Phoenix. У кристалла Strix Point корневой комплекс PCIe меньше, чем у Phoenix, который, в свою очередь меньше, чем у кристалла Cezanne (Ryzen 5000). За последние три поколения процессоров AMD сократила в них количество линий PCIe на четыре. Если Cezanne имеет 24 линии PCIe 3.0 (x16 для видеокарты + x4 для NVMe SSD + x4 для шины чипсета или GPP), то у Phoenix количество линий было сокращено до 20 PCIe 4.0 (x8 для видеокарты + x4 для NVMe SSD + x4 для шины чипсета или GPP + x4 для USB4). А у нового Strix Point количество линий PCIe 4.0 сокращено до 16 (x8 для видеокарты + x4 для NVMe SSD + x4 для USB4 или GPP). Cокращение количества линий PCIe связано с тем, что Strix Point предназначен для конкуренции с Intel Lunar Lake, у которых также есть только четыре линии PCIe для видеокарты или GPP. С выходом процессоров Intel Arrow Lake-H и Arrow Lake-HX компания AMD, как ожидается, выпустит чипы Fire Range, которые получат 28 линий PCIe 5.0 и смогут работать в паре даже с самыми быстрыми дискретными мобильными графическими процессорами. Western Digital показала кристаллы 3D QLC NAND объёмом 2 Тбит — очень ёмкие и доступные SSD уже не за горами

13.06.2024 [19:05],

Сергей Сурабекянц

Western Digital на конференции инвесторов предварительно представила первый в мире кристалл памяти 3D QLC NAND ёмкостью 2 Тбит (256 Гбайт). Новая флэш-память потенциально может изменить рынок твердотельных накопителей, позволяя создавать гораздо более быстрые и энергоэффективные SSD большой ёмкости. Кристалл производится по отработанному 218-слойному производственному процессу BiCS8 и имеет настолько крошечные размеры, что легко помещается на кончике пальца.

Источник изображений: Western Digital «Я очень рад поделиться с вами предварительным обзором кристалла BiCS8 2Tb 3D QLC, — заявил генеральный менеджер подразделения флэш-памяти Western Digital Роберт Содербери (Robert Soderbery). — Мы разработали этот кристалл для удовлетворения потребностей центров обработки данных и систем хранения данных искусственного интеллекта. Вскоре мы собираемся анонсировать этот продукт, но я хочу поделиться им с вами сегодня. Это кристалл памяти с самой высокой ёмкостью в мире». «Обычно мы показываем вам пластину, но мне показалось, что вид пластины не совсем передаёт то, чего мы достигли, — сказал Содербери. — Итак, я хочу показать вам кристалл. Пожалуйста, увеличьте масштаб того, что я держу здесь на пальце. Это размер кристалла, намного меньше чем кончик моего пальца». Микросхема 3D QLC NAND ёмкостью 2 Тбит является огромным достижением по сравнению с «базовым» продуктом 3D TLC ёмкостью 1 Тбит, изготовленном на основе той же 218-слойной производственной технологии BiCS8. На данный момент компания не предоставила информации об архитектуре нового чипа и скоростных характеристиках, но поделилась сравнительными показателями производительности и энергопотребления. 3D QLC NAND ёмкостью 2 Тбит (256 Гбайт) позволит производителям создавать SSD ёмкостью 1 Тбайт, используя всего четыре кристалла памяти. В производители уже научились упаковывать до 16 кристаллов в один корпус — с новыми кристаллами WD можно получить ёмкость 4 Тбайт в одном чипе. Таким образом, если Western Digital и её партнёр Kioxia смогут наладить массовое производство 3D QLC NAND ёмкостью 2 Тбит, новинка может существенно повлиять на стоимость твердотельных накопителей большой ёмкости. Western Digital заявляет, что плотность её кристаллов QLC на 15–19 % выше, чем у конкурентов. По утверждению компании, новинка на 50 % быстрее и требует на 13 % меньше энергии на 1 Гбайт хранимой информации, чем конкуренты. Официальный анонс 3D QLC NAND ёмкостью 2 Тбит ожидается в ближайшее время. На фото показался кристалл мобильных процессоров AMD Phoenix 2 с ядрами Zen 4 и Zen 4c

10.09.2023 [16:15],

Николай Хижняк

Информатор HXL поделился фотографией предполагаемого кристалла мобильного гибридного процессора AMD Phoenix 2, в состав которого входят большие ядра Zen 4, а также вспомогательные ядра общего назначения Zen 4с. Ожидается, что Phoenix 2 в иерархии процессоров AMD будет находиться ниже основной линейки процессоров Ryzen Phoenix.

Источник изображения: @9550pro / X На предоставленном снимке отчётливо виден большой блок кеш-памяти L3 (выделен зелёным цветом в левой части фото), два высокопроизводительных ядра Zen 4 (под кешем L3), четыре малых ядра Zen 4c (три выше кеш-памяти L3, одно рядом с ядрами Zen 4), а также большой блок встроенного ГП (на правой стороне фото). В верхней части кристалла расположены интерфейсы DDR5/LPDDR5 PHY, в нижней и левой части APU расположились интерфейсы PCIe, USB и других физических разъёмов. Оригинальные процессоры AMD Ryzen 7040 (Phoenix) предлагают восемь высокопроизводительных ядер Zen 4. Phoenix 2 имеет только шесть ядер — два больших Zen 4 и четыре энергоэффективных Zen 4c, что позволило сократить общую площадь кристалла. Это намекает на то, что Phoenix 2 будут использоваться в недорогих моделях ноутбуков. Что ещё AMD отрезала от процессора, чтобы сделать его более доступным — неизвестно. Узнаем на момент анонса указанных чипов. Предполагается, что первые гибридные процессоры AMD с разными ядрами должны составить конкуренцию младшим моделям процессоров Intel Alder Lake и Raptor Lake в сегменте ноутбуков. Комбинируя высокопроизводительные и энергоэффективные ядра, компания может добиться ранее недостижимых показателей энергоэффективности своих процессоров. Анонс Phoenix 2 ожидался в этом году. Однако по состоянию на сентябрь официальных данных о них по-прежнему нет. Возможно, компания решила сделать их частью будущей серии процессоров Ryzen 8000, которая ожидается в 2024 году. В таком случае им придётся конкурировать с младшими моделями Intel Meteor Lake. Учёные получили новое состояние вещества — они собрали субатомные квазичастицы в сверхплотный кристалл

22.06.2023 [13:51],

Павел Котов

Учёные Калифорнийского университета в Санта-Барбаре пропустили мощный луч света через два химических соединения и открыли экзотический материал из субатомных квазичастиц. Новый материал они назвали «бозонным коррелированным изолятором» — это высокоупорядоченный кристалл из экситонов, которые относятся к субатомным квазичастицам. И он представляет собой новое состояние вещества.

Формирование кристалла электронами и «дырками» — художественная иллюстрация. Источник изображения: ucsb.edu Субатомные частицы можно разделить на фермионы и бозоны. Они отличаются друг от друга спином и особенностями взаимодействия. Фермионы, а это, например, кварки и электроны, рассматриваются как строительные блоки материи — из них образуются атомы, а частицы эти характеризуются полуцелым спином. Бозоны же являются переносчиками взаимодействия — к ним, в частности, относятся фотоны — и считаются своего рода клеем Вселенной, поскольку связывают воедино фундаментальные силы природы. Эти частицы имеют целые спины; несколько бозонов могут находиться в одной и той же точке пространства одновременно, тогда как фермионы собираться вместе «не любят». При этом известен случай, когда два фермиона образуют бозон. Если отрицательно заряженный электрон образует связь с положительно заряженной «дыркой» (квазичастицей), то вместе они формируют бозонную квазичастицу, называемую экситоном. Американские учёные решили изучить взаимодействие экситонов, наложив решётку дисульфида вольфрама на аналогичную решётку диселенида вольфрама и образовав узор, который называется муаром. Далее на обе решётки учёные направили сильный луч света, из-за чего экситоны начали активно сталкиваться и образовали новую кристаллическую материю с нейтральным зарядом — бозонный коррелированный изолятор. Исследователи отметили, что это новое состояние вещества впервые было создано в системе «реальной» материи, а не синтетической системе, что даёт ключи к новому пониманию поведения бозонов. И прокладывает пути к созданию бозонных материалов нового типа. |