|

Опрос

|

реклама

Быстрый переход

Передовой 1,8-нм техпроцесс Intel 18A не готов к массовому производству, показали тесты Broadcom

04.09.2024 [19:14],

Анжелла Марина

Intel столкнулась с неприятным сюрпризом в рамках своего проекта по развитию контрактного производства чипов, который был запущен в 2021 году. Тесты компании Broadcom показали, что передовой технологический процесс Intel 18A не готов к массовому производству.

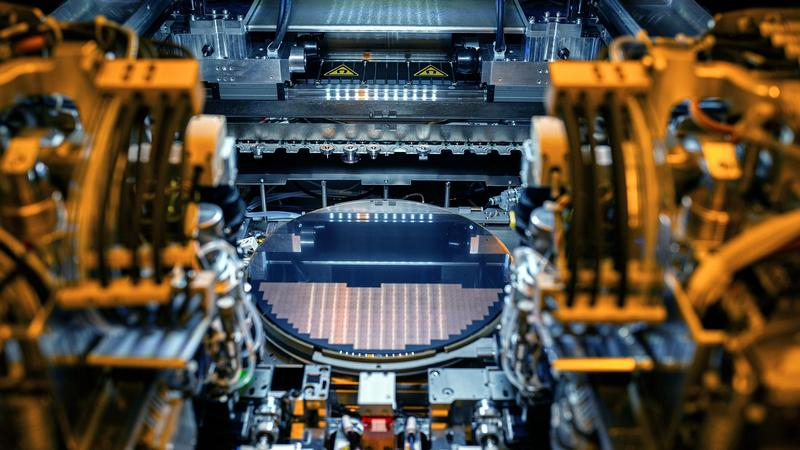

Источник изображения: Intel По информации Reuters, испытания передового производственного процесса Intel 18A, проведённые одним из ключевых игроков в сфере сетевого оборудования и радиочипов, компанией Broadcom, оказались неудачными. Broadcom получила от Intel кремниевые пластины с полупроводниками, выполненными по технологии Intel 18A. Но после изучения этих пластин инженеры и руководство Broadcom пришли к выводу, что процесс 18A пока не готов к массовому производству. Неудачные тесты Broadcom нанесли удар по планам Intel по развитию контрактного производства чипов, так как Intel, под руководством нового генерального директора Пэта Гелсингера (Pat Gelsinger), рассматривает контрактное производство как ключевой элемент стратегии по восстановлению своих позиций. Компания вложила около $100 млрд в расширение производственных мощностей на территории США и рассчитывает привлечь крупных контрактных клиентов, таких как Nvidia или Apple, чтобы заполнить эти мощности. Однако, несмотря на заявления представителя Intel о том, что с технологией 18A всё в порядке, и о наличии «большого интереса со стороны отрасли», компания Broadcom пока не готова делать окончательные выводы о сотрудничестве. «Мы оцениваем все предложения Intel Foundry и ещё не завершили эту оценку», — заявил представитель Broadcom. Ситуация осложняется текущими финансовыми трудностями Intel. Во втором квартале компания зафиксировала операционные убытки в подразделении Foundry в размере $7 млрд, что превышает убытки прошлого года в $5,2 млрд, а руководство Intel прогнозирует выход на безубыточность в этом бизнесе только к 2027 году. В условиях падения рыночной капитализации и сокращения инвестиций в строительство новых производств, неудача с Broadcom может ещё больше осложнить ситуацию, тем более на фоне сокращения 15 % рабочих мест и пересмотре капитальных затрат. В середине сентября совет директоров компании рассмотрит ещё один план по сокращению расходов в отдельных бизнес-подразделениях. Что касается компании Broadcom, она хоть и не столь известна широкой публике, является крупным производителем сетевого оборудования и радиочипов, её выручка от продаж чипов в прошлом финансовом году составила $28 млрд. Компания активно участвует в проектах, связанных с искусственным интеллектом, а аналитик J.P. Morgan Харлан Сур (Harlan Sur) прогнозирует, что в этом году её доходы от ИИ составят 11-12 миллиардов долларов, по сравнению с $4 млрд в прошлом году. Интересно, что Broadcom сотрудничает с Google (Alphabet) и Meta✴ Platforms в производстве их собственных процессоров для ИИ, что может включать в себя заключение контрактов с производителями, в том числе с Intel или TSMC. Несмотря на трудности, Intel продолжает продвигать свой техпроцесс 18A. Компания выпустила набор инструментов для других производителей чипов и, по словам Гелсингера, около десятка клиентов уже активно изучают его. Intel планирует завершить подготовку производства к концу года и начать серийный выпуск чипов в 2025 году. Однако, ситуация с Broadcom показывает, что переход на новую технологию сопряжён с рисками и может отпугнуть потенциальных клиентов, особенно учитывая стоимость производства на передовых технологических узлах, которая исчисляется несколькими десятками тысяч долларов только за одну пластину. Чиплеты AMD с ядрами Zen 5 содержат 8,315 млрд транзисторов — плотность выросла на 28 %

18.07.2024 [19:53],

Николай Хижняк

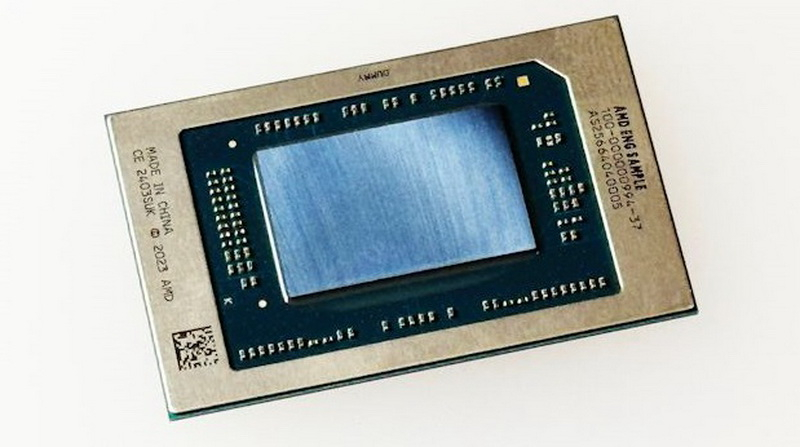

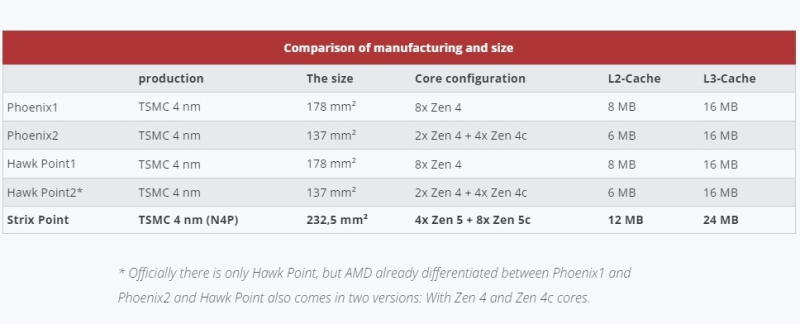

В конце июля компания AMD выпустит две серии процессоров — настольные Ryzen 9000 (Granite Ridge) и мобильные Ryzen AI 300 (Strix Point) — на базе новейшей архитектуры Zen 5. Портал HardwareLuxx.de выяснил недостающие подробности об этих процессорах. В частности, стали известны размеры кристаллов данных чипов и количество используемых в них транзисторов.

Источник изображения: AMD Процессоры Ryzen AI 300 (Strix Point) построены на монолитном кристалле, который производится с использованием 4-нм техпроцесса N4P компании TSMC. Это немного улучшенная версия техпроцесса N4, на базе которого выпускаются процессоры AMD Phoenix и Hawk Point на архитектуре Zen 4. Площадь кристалла Strix Point составляет 232,5 мм2. Таким образом, он значительно больше кристаллов Hawk Point и Phoenix с площадью 178 мм2.

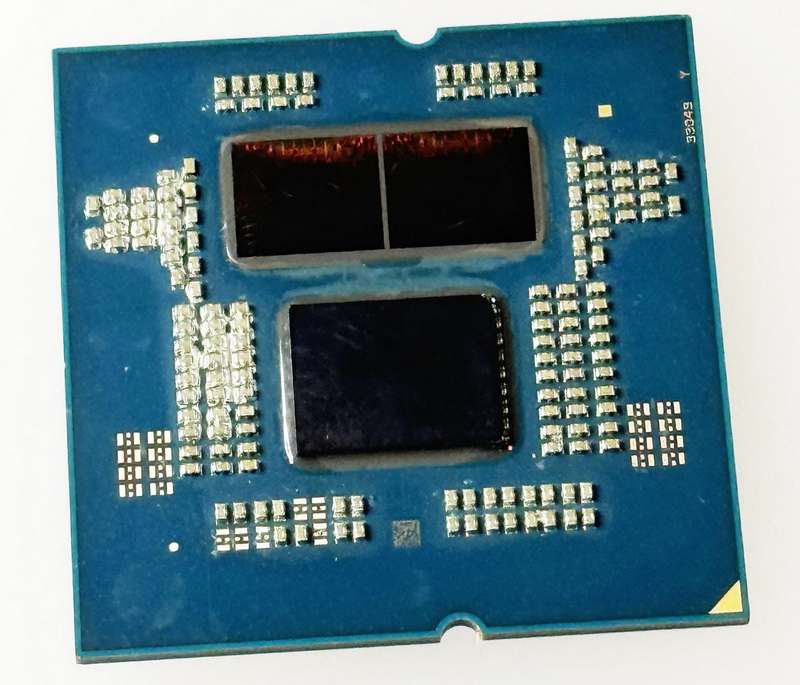

Источник изображения: HardwareLuxx.de Выросшая площадь кристалла Strix Point объясняется увеличившимся количеством исполнительных блоков встроенной графики Radeon 800M на новой архитектуре RDNA 3.5 с 8 до 12 у модели Ryzen AI 9 365 и с 12 до 16 у Ryzen AI 9 HX 370. Также площадь нового кристалла стала больше из-за увеличившегося до 24 Мбайт объёма кеш-памяти L3 и в целом из-за более крупных ядер Zen 5 и Zen 5c. Настольные процессоры Ryzen 9000 (Granite Ridge) используют чиплетную компоновку, как у Ryzen 7000 (Raphael). AMD подтвердила, что в новых процессорах используется блок ввода-вывода I/O die (cIOD) от Raphael, производящийся с использованием того же 6-нм техпроцесса. Площадь этого кристалла не изменилась и составляет 122 мм2. В нём содержатся 3,4 млрд транзисторов. Для сравнения, cIOD процессоров Ryzen 5000 (Vermeer) и Ryzen 3000 (Matisse) производились с применением 12-нм техпроцесса компании Global Foundries и обладали площадью 125 мм2, но содержали значительно меньшее количество транзисторов — 2,09 млрд. Ключевым фактором увеличения площади кристалла cIOD стал встроенный в него блок iGPU с двумя исполнительными блоками.  В процессорах Ryzen 9000 используется новый кристалл CCD с восемью вычислительными ядрами, получивший название Eldora. По данным HardwareLuxx.de, он производится на базе того же 4-нм техпроцесса N4P, что и кристаллы процессоров Strix Point. Однако согласно другим источникам, эти чипы могут производиться с использованием ещё более передового техпроцесса N4X, лучше работающего с высокими тактовыми частотами.

Источник изображения: HardwareLuxx.de В самом кристалле CCD процессоров Ryzen 9000 присутствуют 8,315 млрд транзисторов, что является значительным приростом по сравнению с 6,5 млрд транзисторов в составе восьмиядерного кристалла CCD Durango чипов Ryzen 7000 на архитектуре Zen 4. Примечательно, что несмотря на увеличившееся на 28 % количество транзисторов, площадь CCD Eldora на базе Zen 5 на 0,5 % меньше, чем площадь CCD Durango на Zen 4 — 70,6 мм2 против 71 мм2. Напомним, что CCD Durango на Zen 4 производится с применением 5-нм техпроцесса TSMC N5.

Источник изображения: HardwareLuxx.de Таким образом, общее количество транзисторов в составе флагманского 16-ядерного процессора Ryzen 9 9950X с двумя чиплетами CCD составляет 20,03 млрд. В свою очередь Ryzen 7 9700X с одним CCD содержит 11,715 млрд транзисторов. Samsung представила свой первый 3-нм процессор — Exynos W1000 для будущих смарт-часов

03.07.2024 [13:44],

Николай Хижняк

Компания Samsung представила Exynos W1000 — первый процессор, выпускающийся с использованием её фирменного 3-нм технологического процесса производства. Предполагается, что чип станет основной для новых смарт-часов Galaxy Watch 7 и Galaxy Watch Ultra, анонс который состоится на следующей неделе.

Источник изображений: Samsung Samsung сообщила, что Exynos W1000 выполнен с использованием её 3-нм техпроцесса второго поколения (вероятно, SF3). В составе процессора имеются одно ядро Cortex-A78, четыре Cortex-A55, GPU Mali-G68 MP2, поддерживающий экраны с разрешением до 640 × 640 пикселей, а также 32 Гбайт встроенной памяти. По словам компании, новый чип обеспечивает в 2,7 раза более быстрый запуск приложений по сравнению с Exynos W930, а его многопоточная производительность в 3,7 раза выше, чем у предшественника. Для уменьшения размера чипа, повышения его производительности и энергоэффективности Samsung использовала много новых технологий в Exynos W1000. Например, в нём задействуется технология упаковки FOPLP (Fan-Out Panel Level Packaging) для повышения энергоэффективности и лучшего рассеивания тепла. Для оснащение процессора встроенной оперативной и постоянной памятью использовалась технология упаковки ePOP (Package-on-Package). Кроме того, в новом процессоре применяется технология SiP (System-in-Package), благодаря которой в него интегрирован модуль управления питанием (PMIC). Для Exynos W1000 заявляется поддержка технологии 2.5D Always on Display (AoD), которая обеспечивает более качественное отображение изображения и цветов в режиме постоянно включённого дисплея. Кроме того, чип поддерживает Bluetooth LE для передачи звука и энергоэффективную оперативную память стандарта LPDDR5. Для новинки также заявляется поддержка 4G LTE, Bluetooth, Wi-Fi b/g/n, GPS и NFC. Согласно предыдущим слухам и утечкам, Exynos W1000 станет основной для смарт-часов Galaxy Watch 7 и Galaxy Watch Ultra, анонс которых ожидается на следующей неделе. Отмечается, что благодаря новым технологиям в составе Exynos W1000 эти устройства Samsung смогут работать в течение 2–3 дней от одного заряда батареи. Google откажется от услуг Samsung и поручит производство чипов Tensor G5 компании TSMC

20.06.2024 [18:11],

Николай Хижняк

Компания Google с 2025 будет выпускать свои фирменные процессоры Tensor на мощностях TSMC, сообщают сразу несколько источников. Первое поколение чипов Tensor компания представила в 2021 году в серии смартфонов Pixel 6. С тех пор данные процессоры производились по заказу компанией Samsung.

Источник изображения: Google Как сообщается, десятое поколение смартфонов Pixel будут работать на чипах Tensor G5, которые будут производиться с применением 3-нм техпроцесса TSMC. Соглашение о сотрудничестве между двумя компаниями было подписано ещё в июле 2023 года, сообщают источники. Актуальный Tensor G3 производится с применением 4-нм техпроцесса Samsung. Процессор Tensor G4, который ляжет в основу смартфонов серии Pixel 9, всё ещё будет выпускаться компанией Samsung, а вот его преемник станет первым процессором Google для мобильных устройств, которые будет поручено выпускать тайваньской компании TSMC. Как сообщает Business Korea, переход на новый техпроцесс для Tensor G5 неизбежен, поскольку все основные конкуренты Google, включая Qualcomm и MediaTek, будут выпускать свои будущие процессоры на 3-нм техпроцессе. А та же Apple использует 3-нм техпроцесс для производства процессоров для iPhone 15 Pro с 2023 года. В том же отчёте южнокорейского издания говорится, что Samsung тем временем борется с проблемами производительности и энергоэффективности своего флагманского мобильного чипа Exynos 2500. Сообщается, что энергопотребление и тепловыделение чипа примерно на 10-20 % выше, чем у чипов, выпускаемых согласно 3-нм процессу TSMC. По мнению ведущего аналитика Мин-Чи Куо (Ming-Chi Kuo), по этой причине Samsung может отказаться от использования Exynos 2500 в составе будущей линейки смартфонов Galaxy S25 в пользу процессоров Qualcomm Snapdragon. TSMC уверена в запуске 2-нм техпроцесса в следующем году, а Samsung намерена ускорить освоение 1-нм технологии

28.05.2024 [23:18],

Николай Хижняк

Тайваньский контрактный производитель чипов TSMC рассказал о том, как идёт освоение 2-нм технологического процесса производства микросхем. Компания уверена в успехе новой технологии — она считает, что 2-нм техпроцесс привлечёт больше клиентов, чем 3-нм.

Источник изображения: Business Korea Выступая на технологическом форуме 23 мая, вице-президент TSMC Чжан Сяоган (Zhang Xiaogang) заявил, что «развитие 2-нм техпроцесса идёт гладко» и что «массовое производство чипов по нормам 2-нм должно стать возможным примерно в 2025 году, как и планировалось», пишет тайваньское издание Industrial and Commercial Times. Таким образом, заявление топ-менеджера TSMC опровергает ранее ходившие слухи о том, что массовое производство чипов на основе 2-нм техпроцесса из-за технических проблем начнётся не раньше 2026 года. Слухи о том, что TSMC откладывает запуск 2-нм техпроцесса возникли на фоне того, что этот техпроцесс предполагает переход к производству транзисторов с круговым затвором GAA (Gate-All-Around). Эта технология была представлена компанией Samsung в 2022 году, когда производитель анонсировал переход к массовому производству чипов с применением 3-нм техпроцесса. GAA позволяет снизить утечку тока в транзисторах, повысив тем самым энергоэффективность чипов в целом. По словам Чжана Сяогана, «выход годной продукции с применением технологии GAA достиг 90 % от целевого показателя». «Спрос на 2-нм техпроцесс превысит спрос на 3-нм и 5-нм техпроцессы», — в свою очередь выразил уверенность генеральный директор TSMC Вэй Чжэцзя (Wei Zhejia). Он добавил, что компания также планирует к концу года утроить производственные мощности для выпуска 3-нм продуктов, но даже в этом случае не сможет покрыть все заказы. Уверенность TSMC в успехе нового техпроцесса объясняется её сотрудничеством с Apple — самым крупным клиентом TSMC, на которого приходится до 25–30 процентов заказов. Ранее сообщалось, что операционный директор Джефф Уильямс (Jeff Williams) недавно посетил Тайвань для проведения переговоров с TSMC о перспективе выпуска ИИ-чипов. По данным издания Business Korea, компания Samsung планирует провести 12–13 июня в Кремниевой долине мероприятие Foundry and SAFE Forum, на котором, как ожидается, представит новую технологическую «дорожную карту» и сообщит о переносе старта массового производства чипов по нормам 1 нм с 2027 на 2026 год. TSMC запустит массовое производство по оптимизированному 3-нм техпроцессу N3P уже в этом году

16.05.2024 [22:06],

Сергей Сурабекянц

На традиционном весеннем технологическом симпозиуме TSMC представила обновлённую информацию о состоянии своих текущих и будущих 3-нм техпроцессов. Технология N3E применяется в серийном производстве с четвёртого квартала 2023 года, в этом году будет запущено массовое производство по техпроцессу N3P, который сохранит преемственность по технологической оснастке и средствам проектирования. Кроме того, N3P призван обеспечить снижение уровня брака при производстве чипов.

Источник изображения: TSMC TSMC сообщает о высоком уровне выхода годной продукции у 3-нм технологического процесса второго поколения N3E. По данным компании, плотность дефектов D0 в N3E находится на одном уровне с 5-нм техпроцессом N5. Это немалое достижение, учитывая дополнительные сложности, связанные с разработкой последнего, ещё более совершенного поколения технологии FinFET. Передовые клиенты TSMC, такие как Apple, только что выпустившая процессор M4, смогут относительно быстро воспользоваться преимуществами улучшенного технологического узла. Техпроцесс N3E представляет собой упрощённую версию N3B, в которой исключены некоторые уровни EUV и не используется двойное экспонирование. Это снижает себестоимость производства и увеличивает производительность, хотя за это приходится платить некоторым снижением плотности транзисторов. В отличие от оригинального N3B, чей производственный цикл будет относительно коротким, поскольку единственным его крупным заказчиком выступила Apple, N3E будет востребован широким кругом клиентов TSMC, в том числе многими крупнейшими разработчиками чипов. На сегодняшний день N3P завершил весь квалификационный цикл испытаний, по данным компании его показатели выхода годной продукции будут близки к N3E. Благодаря применению оптической усадки, техпроцесс N3P позволяет разработчикам процессоров либо увеличивать производительность на 4 % при тех же токах утечки, либо снижать энергопотребление на 9 % при тех же тактовых частотах. N3P также призван увеличить плотность транзисторов на 4 % для «смешанной» конструкции чипа, к которой TSMC относит процессоры, состоящие на 50 % из логических схем, на 30 % из SRAM и на 20 % из аналоговых схем. Поскольку N3P является дальнейшим развитием N3E, он совместим со своим предшественником с точки зрения IP-блоков, правил процессов, инструментов разработки и методологии электронного проектирования (EDA). TSMC ожидает, что к концу года на большей части производства будет использоваться N3P, так как он обеспечивает более высокую производительность при меньших затратах. Samsung расскажет о GAA-транзисторах третьего поколения для 2-нм чипов в июне

30.04.2024 [23:00],

Николай Хижняк

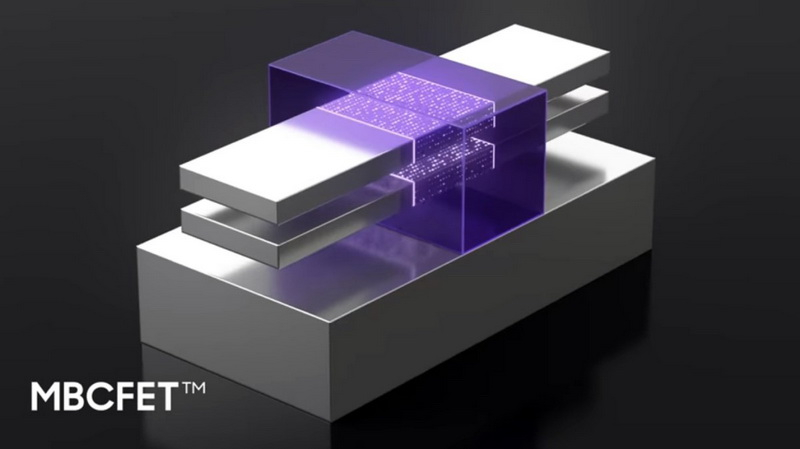

Компания Samsung разрабатывает транзисторы GAA (Gate-all-Around) нового поколения, которые будут применяться в чипах, производимых по её 2-нм техпроцессе. Компания планирует внедрить технологию в следующем году. Об этом сообщает южнокорейское издание Business Korea, ссылающееся на свои источники в отрасли.

Источник изображений: Samsung Со ссылкой на свои источники издание также отмечает, что Samsung собирается представить доклад о третьем поколении технологии GAA для своего 2-нм техпроцесса (SF2) в рамках конференции по вопросам полупроводниковых технологий VLSI Symposium 2024, которая будет проходить на Гавайях с 16 по 20 июня. Технология GAA, которую первой в мире поставила на коммерческие рельсы именно компания Samsung, это технология производства транзисторов с затвором, который полностью окружает канал. Поскольку с каждым переходом на новый техпроцесс транзисторы в составе полупроводника становятся меньше, контролировать движение тока в них становится всё сложнее. Однако GAA предлагает совершенно новую архитектуру транзистора, которая позволяет повысить его энергоэффективность. В настоящий момент Samsung является единственной компанией в мире, которая может массово применять технологию GAA-транзисторов для производства чипов. Она приступила к исследованию GAA ещё в начале 2000-х годов и впервые внедрила её для своего 3-нм техпроцесса в 2022 году. Однако из-за мировой экономической нестабильности, высокой стоимости производства, а также ограниченной клиентской базы в таких секторах, как мобильные устройства, спрос на 3-нм техпроцесс Samsung оказался несущественным. Как результат, лидерство в производстве 3-нм чипов перешло к тайваньскому контрактному производителю чипов TSMC, который использует более традиционные (и дешёвые) методы производства транзисторов. В ответ Samsung готовит второе поколение транзисторов GAA для 3-нм техпроцесса, которое она собирается представить в течение этого года. А в следующем году компания представит третье поколение GAA для 2-нм техпроцесса, чтобы закрепить лидерство в этом направлении. TSMC и Intel тоже планируют в конечном итоге перейти на использование технологии GAA с переходом на 2-нм техпроцесс производства, но случится это позже, чем у Samsung. Таким образом, у южнокорейской компании будет некое преимущество перед конкурентами. По крайней мере в теории. Официальное название технологии GAA от Samsung — MBCFET. Первое поколение GAA для техпроцесса 3 нм по сравнению с предыдущим поколением FinFET-транзисторов Samsung обеспечило 23-процентную прибавку в производительности, 16-процентное увеличение плотности и 45-процентное повышение энергоэффективности. Второе поколение GAA для 3 нм техпроцесса, как ожидается, обеспечит 30-процентную прибавку в производительности, 35-процентное повышение плотности, а также 50-процентное снижение в энергопотреблении. Что касается третьего поколения MBCFET, то для него также ожидается значительная прибавка в производительности с более чем 50-процентным повышением энергоэффективности по сравнению с предыдущим поколением технологии. TSMC научилась создавать монструозные двухэтажные процессоры размером с пластину

26.04.2024 [21:18],

Николай Хижняк

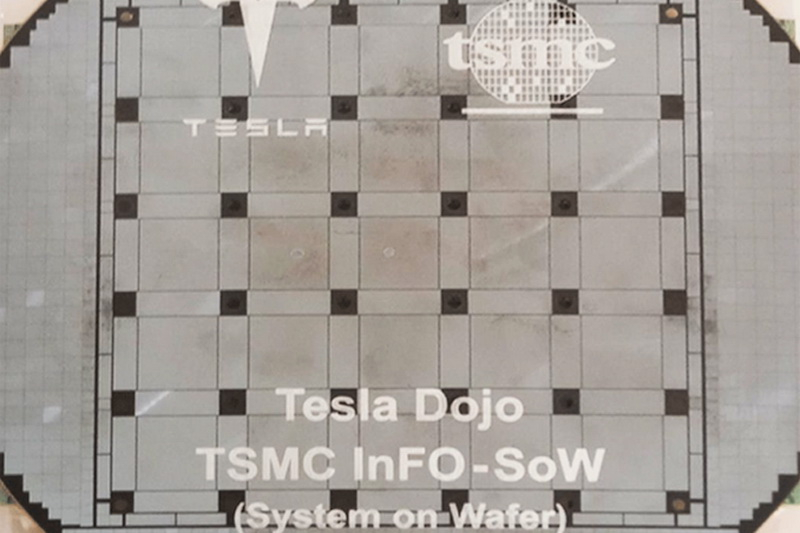

Компания TSMC представила новое поколение платформы «система-на-пластине» (System-On-Wafer) CoW-SoW, в которой применяется технология 3D-компоновки. Основой CoW-SoW является платформа InFO_SoW, представленная компанией в 2020 году, и позволяющая создавать логические процессоры в масштабе целой 300-мм кремниевой пластины. К настоящему моменту только компания Tesla адаптировала эту технологию. Она применяется в её суперкомпьютере Dojo.

Источник изображений: TSMC В новой платформе CoW-SoW компания TSMC собирается объединить два метода упаковки — InFO_SoW и System on Integrated Chips (SoIC). Благодаря использованию технологии Chip-on-Wafer (CoW) метод позволит размещать память и/или логику непосредственно поверх «системы на пластине». Ожидается, что новая технология CoW-SoW будет готова к массовому производству к 2027 году. «В будущем метод интеграции в масштабе пластины позволит нашим клиентам объединять ещё больше логических компонентов и памяти. Технология SoW — больше не фикция. Это то, над чем мы уже работаем с нашими клиентами для дальнейшей перспективы её использования в их существующих продуктах. Мы считаем, что передовая технология интеграции на уровне пластин предоставит нашим клиентам возможность продолжать наращивать вычислительные мощности их ИИ-систем или суперкомпьютеров», — сказал Кевин Чжан, вице-президент по развитию бизнеса в TSMC. Сейчас TSMC рассматривает возможность объединения в рамках платформы CoW-SoW логических процессоров с высокопроизводительной памятью HBM4. Последняя будет иметь 2048-битный интерфейс и располагаться непосредственно поверх логических микросхем. В то же время возможность размещения дополнительной логики на пластине позволила бы оптимизировать производственные издержки. Процессоры масштаба целой кремниевой пластины (например, WSE компании Cerebras), а также процессоры на платформе InFO_SoW обеспечивают значительные преимущества в вопросе производительности и эффективности за счёт высокой пропускной способности, низкой задержки в межъядерных связях, низкого сопротивления при передаче энергии и высокой энергоэффективности. В качестве дополнительного «бонуса» такие процессоры предлагают возможность размещения огромного количества вычислительных ядер. Однако у той же технологии InFO_SoW имеются и некоторые ограничения. Например, эффективность процессоров масштаба кремниевой пластины может ограничиваться эффективностью набортной памяти. Платформа CoW-SoW позволяет обойти это ограничение, поскольку в ней планируется применение высокопроизводительной памяти HBM4. В дополнение к этому обработка пластин InFO_SoW осуществляется с применением только одного технологического процесса, и он не поддерживает трёхмерную компоновку. Этот вопрос позволяет решить новая платформа CoW-SoW. TSMC представила техпроцесс N4C — благодаря ему 4-нм чипы станут дешевле

26.04.2024 [01:15],

Николай Хижняк

Компания TSMC представила новый техпроцесс класса 4–5 нм — N4C. Он призван снизить себестоимость продукции на его основе на 8,5 % по сравнению с процессом N4P, при этом сохранив преемственность по технологической оснастке и средствам проектирования. Кроме того, N4C призван обеспечить снижение уровня брака при производстве чипов. Источник изображений: TSMC «Мы пока не закончили с нашими 5-нм и 4-нм технологиями. При переходе с N5 на N4 мы добились 4-процентной оптической усадки и продолжили улучшать характеристики транзисторов. Теперь мы добавляем N4C в наш портфель технологий 4 нм. N4C позволяет нашим клиентам сократить расходы за счёт сокращения количества используемых масок, а также улучшения исходной конструкции полупроводников, например, стандартных ячеек и SRAM, чтобы ещё больше снизить общие эксплуатационные издержки», — заявил Кевин Чжан (Kevin Zhang), старший вице-президент по развитию бизнеса TSMC на недавно состоявшемся Североамериканском технологическом симпозиуме. Узел N4C является частью семейства техпроцессов TSMC N5/N4 и основан на технологии N4P. Внедрение новой технологии является важным стратегическим шагом для TSMC, поскольку N4C даёт возможность значительно снизить затраты на производство продуктов на основе 4-нм техпроцесса и тем самым стимулировать расширение базы клиентов компании, желающих перейти на новый и недорогой техпроцесс. Новая технология предлагает баланс между энергоэффективностью, производительностью и стоимостью внедрения. Учитывая высокие затраты, связанные с нормами класса 3 нм, и их относительно ограниченные преимущества перед такими технологиями, как N4P, с точки зрения производительности и плотности транзисторов, N4C может стать весьма популярным выбором среди клиентов TSMC. Компания планирует начать массовое производство чипов с использованием техпроцесса N4C в 2025 году. К тому моменту за плечами TSMC будет шесть лет производства продуктов на основе 5-нм техпроцессов. Производитель ожидает, что к этому времени он сможет выйти на хороший уровень выпуска качественной продукции на основе N4C и снизить её стоимость. А поскольку к 2025 году многие инструменты для выпуска продуктов на основе 5-нм техпроцесса «устареют», N4C и аналогичные узлы могут оказаться чуть ли не единственными экономически доступными альтернативами. ASML создала первый образец полупроводника с применением литографии High-NA EUV

17.04.2024 [22:13],

Николай Хижняк

Нидерландская компания ASML сообщила о создании первых образцов полупроводниковых изделий с помощью своего первого литографического сканера со сверхжёстким ультрафиолетовым излучением и проекционной оптикой с высокой числовой апертурой со значением 0,55 (High-NA EUV). Событие является важной вехой не только для ASML, но и для технологии High-NA EUV в целом.

Источник изображения: ASML «Наша High-NA EUV-система в Вельдховене напечатала первые в мире линии плотностью 10 нанометров. Визуализация была сделана после того, как оптика, датчики и стадии прошли процесс грубой калибровки. Далее планируется доведение системы до полной производительности и получение тех же результатов в полевых условиях», — говорится в заявлении ASML. В настоящее время ASML создала всего три литографические системы High-NA EUV. Одна собрана в штаб-квартире компании ASML в Вельдховене (Нидерланды), другую собирают на американском заводе Intel D1X недалеко от Хиллсборо, штат Орегон. Третья будет собрана в Imec, ведущем научно-исследовательском институте полупроводников в Бельгии. Похоже, ASML стала первой компанией, объявившей об успешном создании образцов с использованием системы литографии High-NA EUV, что является важной вехой для всей полупроводниковой промышленности. ASML собирается использовать свой сканер Twinscan EXE:5000 только для исследования и совершенствования технологии. В свою очередь, Intel планирует использовать Twinscan EXE:5000, чтобы научиться применять EUV-литографию с высокой числовой апертурой для массового производства чипов. Сканер будет применяться для R&D-проектов с использованием её фирменного техпроцесса Intel 18A (класс 1,8 нм). А вот сканер следующего поколения, Twinscan EXE:5200, планируется задействовать для производства чипов согласно техпроцессу 14A (класс 1,4 нм). Сканер ASML Twinscan EXE:5200, оснащённый оптикой с числовой апертурой 0,55, предназначен для нанесения элементов чипов с разрешением 8 нм, что является значительным улучшением по сравнению с текущими EUV-системами, обеспечивающими разрешение 13 нм. Новая технология позволяет сократить размеры транзисторов в 1,7 раза и обеспечить увеличение их плотности в 2,9 раза за одну экспозицию по сравнению с инструментами с низкой числовой апертурой (Low-NA EUV). Сканеры с низкой числовой апертурой тоже позволяют добиться такого уровня разрешения, однако в таком случае требуется использование более дорогостоящего метода двойного шаблона. Переход на системы с литографией High-NA EUV необходим для выпуска чипов согласно нормам ниже 3 нм, массовое производство которых планируется начать в 2025–2026 годах. Применение High-NA EUV-литографии позволяет исключить необходимость в использовании двух проходов с двумя шаблонами, тем самым оптимизировать производственные процессы, потенциально повысив производительность и сократив производственные расходы. С другой стороны, инструменты с высокой числовой апертурой стоят до 400 миллионов долларов каждый и имеют свои недостатки, которые усложняют переход к более совершенным технологическим процессам. Samsung объявила о планах по выпуску памяти 3D DRAM, но произойдёт это не скоро

04.04.2024 [15:06],

Николай Хижняк

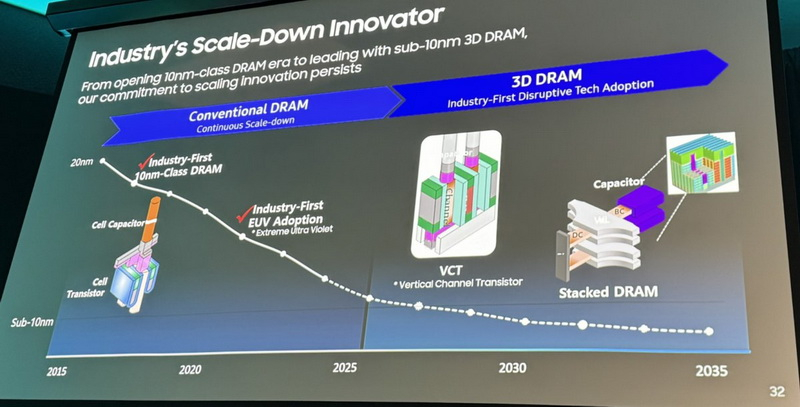

Компания Samsung добавила в свой план по выпуску новых продуктов память 3D DRAM. Информацией об этом производитель поделился на технологической конференции Memcom. Компания планирует представить первый технологический процесс для производства 3D DRAM в течение ближайших четырёх лет.

Источник изображения: Samsung Крупнейший в мире производитель памяти планирует внедрить производство DRAM с транзисторами с вертикальным каналом (VCT) при переходе на техпроцессы тоньше 10 нм для выпуска памяти, следует из слайда компании, продемонстрированного на конференции Memcom. Транзистор с вертикальным каналом (VCT) может представлять собой разновидность FinFET, в котором проводящий канал обёрнут тонким кремниевым «плавником», образующим корпус транзистора. VCT также может представлять собой транзистор с кольцевым затвором (GAA), в котором материал затвора окружает проводящий канал со всех сторон. В случае Samsung речь, судя по всему, идёт о процессе производства DRAM на основе FinFET. От внедрения техпроцесса тоньше 10 нм для производства памяти компанию Samsung отделяет два поколения техпроцессов. Наиболее свежим сейчас является пятое поколение технологии 10-нм класса (фактически 12 нм), которая была представлена в середине 2023 года. Samsung готовит ещё две технологии 10-нм класса, а первое поколение техпроцесса тоньше 10-нм ожидается у производителя во второй половине этого десятилетия.

Источник изображения: Tokyo Electron Применение 3D-транзисторов для DRAM подразумевает создание и применение конструкции ячеек формата 4F2, считающегося с одной из самых эффективных схем расположения ячеек памяти с точки зрения производственных затрат. Производитель оборудования для выпуска чипов, компания Tokyo Electron, ожидает, что производство DRAM с VCT и форматом ячеек 4F2 начнётся в 2027–2028 годах. Компания полагает, что для производства DRAM на основе VCT производителям памяти придётся использовать новые материалы для конденсаторов и разрядных шин. Из предоставленного Samsung изображения планов по выпуску будущих продуктов также становится известно, что компания планирует адаптировать технологию производства многоуровневой памяти DRAM в начале 2030-х, тем самым значительно повысив плотность своих чипов памяти в ближайшие десять лет. Intel анонсировала техпроцесс Intel 14A — его запустят в 2027 году с использованием литографии High-NA EUV

21.02.2024 [22:32],

Андрей Созинов

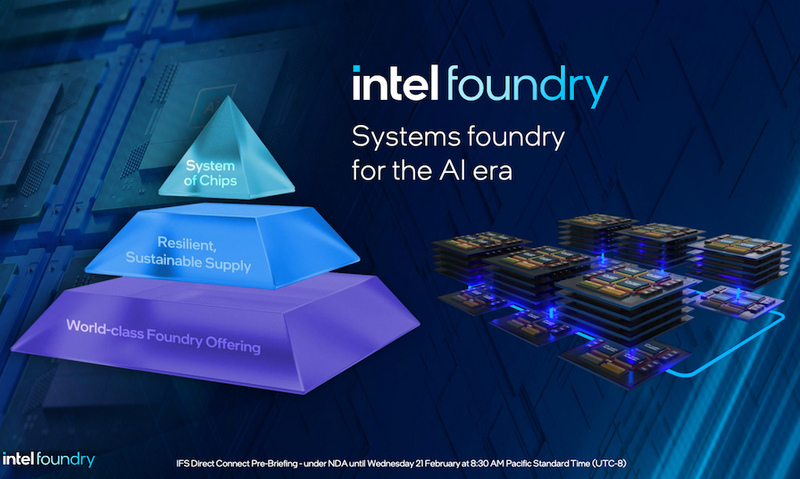

Компания Intel обнародовала свежие планы по освоению передовых техпроцессов. В том числе компания анонсировала 1,4-нм техпроцесс Intel 14A, который станет первой в мире технологией производства чипов с использованием литографии в сверхжёстком ультрафиолете с высокой числовой апертурой (High-NA EUV). Помимо этого, были анонсированы дополнения к представленным ранее планам по запуску техпроцессов.

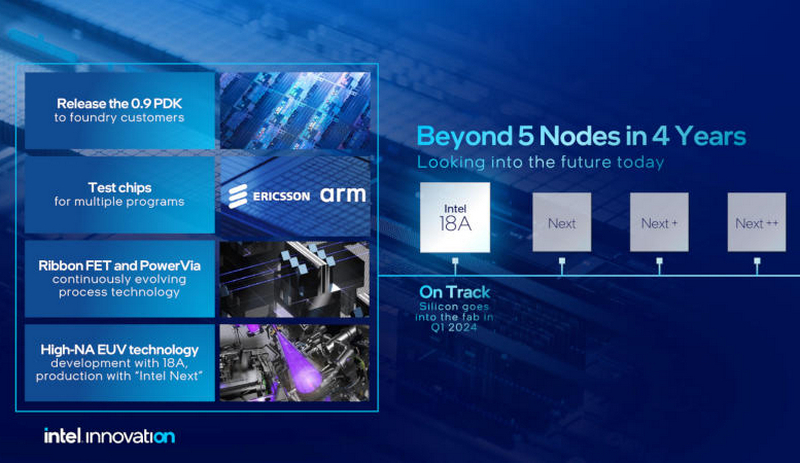

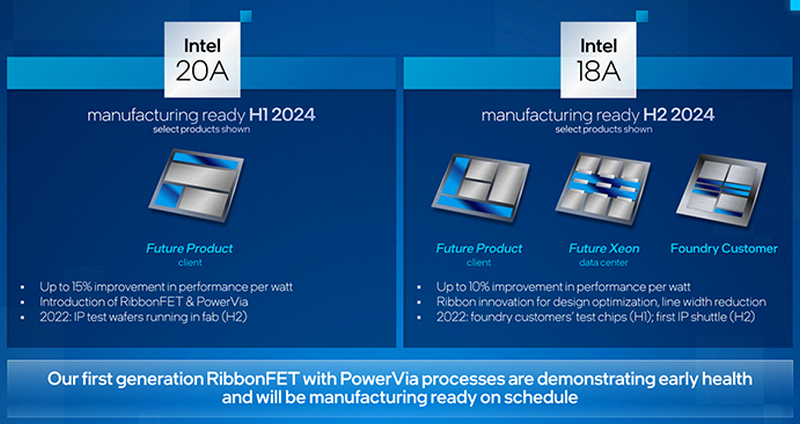

Источник изображений: Intel Первоначальный план генерального директора Intel Пэта Гелсингера (Pat Gelsinger), представленный в 2022 году, который подразумевал освоение пяти техпроцессов за четыре года, остается в силе. Техпроцессы Intel 7 и Intel 4 уже представлены на рынке, а Intel 3 готов к крупносерийному производству. Разработка техпроцессов Intel 20A (2 нм) и 18A (1,8 нм) идёт по плану или даже опережает его. Руководство компании ожидает, что Intel вернет себе лидерство в сфере передовых полупроводников с запуском Intel 18A в 2025 году. Intel уже предоставила партнёрам инструменты для проектирования чипов под техпроцесс 18A в версии PDK 0.9, а финальная версия инструментов PDK 1.0 появится в апреле или мае. Кроме того, Intel уже завершила проектирование серверных процессоров Xeon Clearwater Forest, то есть они фактически готовы к производству. Clearwater Forest — станет первым крупносерийным чипом, выполненным по техпроцессу Intel 18A. Расширенный план по освоению технологических процессов Intel включает новый Intel 14A, а также несколько специализированных версий, представленных ранее техпроцессов. Компания пока не раскрывает целевые показатели производительности и плотности для 14A, заявляя, что пока не хочет ставить конкурентов в известность. Известно, что 1,4-нм чипы Intel будут оснащены системой питания следующего поколения PowerVia (вероятно, Source-on-Contact) и транзисторами RibbonFET GAA. В планах Intel значатся две разновидности 14A: стандартная 14A и последующая улучшенная версия 14A-E, где буква E означает расширение возможностей. Это часть нового подхода Intel к созданию различных модификаций существующих техпроцессов для продления их жизненного цикла, как у TSMC и Samsung. Intel пока не называет точные даты, но известно, что техпроцесс 14A-E будет запущен в тестовое производство в 2027 году. Соответственно можно предположить, что 14A появится в 2026 году, как минимум в тестовом виде, а к 2027-му доберётся до массового производства. Как и другие передовые техпроцессы Intel, новый 14A будет разрабатываться в Орегоне, а затем массово внедряться на других предприятиях. Отметим, что TSMC, по неофициальным данным, начнёт использовать High-NA EUV только к 2030 году, то есть заметно позже Intel. Однако это не значит, что она автоматически отстанет в технологическом плане. Технология High-NA не будет дешевой, и, согласно отраслевым сообщениям, она не так эффективна, как технология Low-NA EUV с двойным шаблонированием. В Intel уверены, что стоимость производства чипов будет соответствовать её ожиданиям, но также отмечают, что при необходимости скорректируют стратегию. Ещё Intel расширит свои техпроцессы Intel 18A, Intel 3, Intel 7 и Intel 16 новыми версиями. Intel планирует запускать новые техпроцессы каждые два года, а затем дополнять их расширениями каждые два года. Дополнительные техпроцессы будут обозначаться суффиксами. Буква P будет указывать на новую версию технологии с улучшенной производительностью. Суффикс T укажет на техпроцессы, оснащенные поддержкой соединения TSV (Through-silicon via), которые могут использоваться в системах с упаковкой 3D Foveros. Суффикс E будет указывать на специализированные новые функции, например, настраиваемый диапазон напряжения. Intel также запустит техпроцессы PT, в которых будет и повышена производительность, и реализована поддержка TSV, а со временем, вероятно, появятся и другие комбинированные решения.  В ближайшее время Intel также запустит техпроцесс Intel 12, который станет результатом производственного сотрудничества с UMC. Ещё отмечается, что Intel Foundry будет выпускать чипы по зрелой 65-нм технологии с помощью Tower Semiconductor. Оба этих сотрудничества имеют ключевое значение для дальнейшего расширения масштабов Intel Foundry, позволяя компании извлекать больше выгоды из уже окупившего себя оборудования и производственных мощностей — они будут заняты делом, а не простаивать. Техпроцессы Intel 20A и Intel 18A предложат транзисторы GAA и подводку питания с обратной стороны кремниевой пластины (BSPDN). Причём последняя из технологий будет реализована на два года раньше TSMC, да и по внедрению GAA компания Intel обгонит тайваньского производителя на 1,5 года. Конечно, это вовсе не значит разгром TSMC — Samsung реализовала GAA ещё раньше, но трудности с массовым производством не позволили реализовать преимущество. И тем не менее, как минимум с технологической точки зрения Intel будет впереди, а это будет хорошим подспорьем для реализации её амбиций на рынке контрактного производства чипов.  Наиболее важным для компании является техпроцесс Intel 18A. И компания уже собрала четыре крупных заказа на производство чипов по данной технологии, и один из них включает большую предоплату, что означает, что речь идет об очень значительном количестве чипов. Ещё сегодня компания Microsoft объявила, что закажет у Intel производство своих чипов по 1,8-нм техпроцессу. Добавим, что Intel преуспела в продвижении техпроцессов Intel 16 и Intel 3, а также заключила крупные сделки на услуги по упаковке чипов. Развитие под санкциями: китайская SMIC разрабатывает технологии выпуска 3-нм чипов без EUV

22.12.2023 [18:50],

Сергей Сурабекянц

Несмотря на отсутствие доступа к оборудованию для выпуска чипов с литографией в экстремальном ультрафиолете (EUV) из-за санкций, китайская компания SMIC продолжает разработку 5-нм и 3-нм техпроцессов производства чипов. Ранее SMIC удалось наладить серийное производство 7-нм микросхем, опираясь исключительно на литографию в глубоком ультрафиолете (DUV), что само по себе не является невозможным — техпроцесс TSMC N7P также не использует EUV.

Источник изображения: SMIC В отчёте Nikkei утверждается, что сразу после запуска 7-нм техпроцесса 2-го поколения, SMIC создала исследовательскую группу для работы над 5-нм и 3-нм техпроцессами. Команду возглавляет ранее работавший в TSMC и Samsung содиректор SMIC Лян Монг-Сонг (Liang Mong-Song). «Нет более умного учёного или инженера, чем этот парень, — так охарактеризовал его Дик Терстон (Dick Thurston), бывший главный юрисконсульт TSMC. — Он действительно один из самых блестящих умов, которых я видел в области полупроводников». SMIC прошла долгий путь от небольшой полупроводниковой фабрики до пятого по величине контрактного производителя микросхем в мире. На фоне растущей напряжённости между США и Китаем компания была включена в санкционный список Министерства торговли США и потеряла доступ к передовым инструментам для обработки кремниевых пластин, что серьёзно замедлило её развитие и внедрение новых технологических процессов. На данный момент литографические машины ASML Twinscan NXT:2000i являются лучшими инструментами, которыми располагает SMIC — они могут производить травление с разрешением до 38 нм. Этот уровень точности обеспечивает экспонирование с шагом 38 нм с использованием двойной фотомаски, чего достаточно для производства чипов класса 7 нм. Согласно исследованиям ASML и IMEC, при 5 нм шаг металла уменьшается до 30-32 нм, а при 3 нм — до 21-24 нм, что уже требует применения EUV.

Источник изображения: ASML Но использование инструментов литографии со сверхвысоким разрешением (13 нм для EUV с низкой числовой апертурой) — не единственный путь к достижению сверхмалых размеров транзисторов. Другой вариант предусматривает нанесение нескольких последовательных масок, но это сложный процесс, который увеличивает продолжительность производственного цикла, снижает процент выхода годных изделий, увеличивает износ оборудования и повышает затраты. Однако без доступа к EUV-литографии у SMIC просто нет другого выбора, кроме как использовать тройное, четверное или даже пятикратное паттернирование. Терстон считает, что под руководством Лян Монг-Сонга SMIC сможет производить (если уже не производит) 5-нм чипы в больших количествах без использования инструментов EUV. Однако сегодняшний отчёт Nikkei впервые сообщает о возможной способности SMIC разработать в обозримом будущем 3-нм производственный процесс на оборудовании класса DUV. «Мы переходим к производству»: Intel завершила разработку ангстремного техпроцесса Intel 18A

07.11.2023 [18:27],

Андрей Созинов

Генеральный директор Intel Патрик Гелсингер (Patrick Gelsinge) заявил, что американская компания следует плану по освоению пяти передовых техпроцессов за четыре года и тем самым убедить клиентов в конкурентоспособности своих технологий. Гелсингер заявил, что самый передовой техпроцесс компании — Intel 18A — перейдет в стадию тестового производства уже в первом квартале 2024 года.  «По поводу 18A, у нас уже выпускается много тестовых пластин, — сказал Гелсингер. — Фаза разработки 18A завершена, и теперь мы переходим к производству». Технологический процесс Intel 18A, что расшифровывается как 18 ангстрем или 1,8 нм, является важнейшим элементом в стратегии Intel по возвращению себе лидерства в производстве полупроводников к 2025 году. Компания также объявила, что будет использовать эту технологию не только для выпуска собственных чипов, но и для производства микросхем для сторонних заказчиков, включая Ericsson и американских оборонных подрядчиков, на контрактной основе.  Samsung и TSMC стремятся запустить массовое производство микросхем по своим 2-нм техпроцессам в 2025 году. Считается, что эти 2-нанометровые чипы будут соответствовать чипам Intel 18A. По словам Гелсингера, с момента его возвращения в компанию в 2021 году Intel активно реализует план «пять техпроцессов за четыре года». Обычно производителю требуется не менее двух лет для перехода на новый техпроцесс. «И вот мы здесь, — сказал Гелсингер. — Прошло два с половиной года с начала этого пути, и знаете что? Это действительно происходит, мы на пути к созданию пяти техпроцессов за четыре года».  План Intel предусматривает освоение технологий производства чипов Intel 7, Intel 4, Intel 3, Intel 20A и Intel 18A. Первые два техпроцесса уже запущены в массовое производство, новейший процессор Meteor Lake основан как раз на технологии Intel 4. По словам Гелсингера, технология Intel 3, которая будет использоваться для следующего поколения чипов для серверов и ПК, сейчас находится на стадии отладки и будет приведена к массовому производству в следующем году. Для Intel будет крайне важно убедить клиентов в преимуществах своей передовой технологии производства. Это нужно для того, чтобы сохранить доминирующее положение в сфере процессоров для ПК и серверов, поскольку в эпоху искусственного интеллекта конкуренция становится ещё более острой. Конкуренты, такие как Qualcomm, стремятся отвоевать долю рынка у Intel в сегменте ПК. Intel впервые за 13 лет изменит транзисторы в чипах — компания показала RibbonFET и схему их обратного питания

20.09.2023 [11:15],

Геннадий Детинич

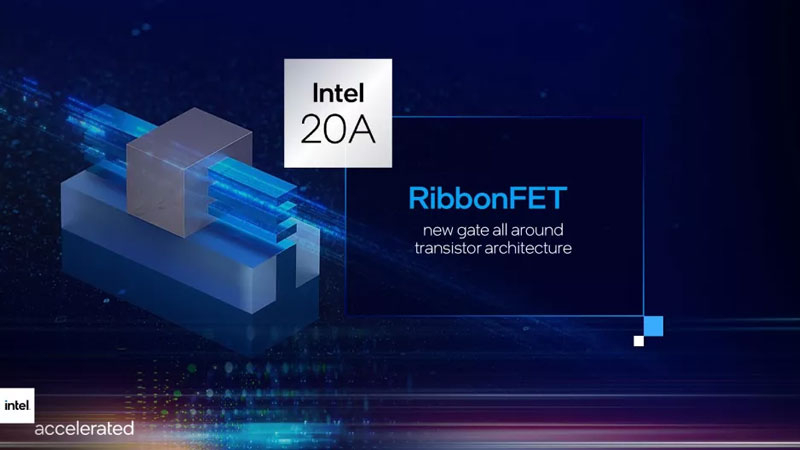

На конференции Innovation 2023 глава компании Intel Патрик Гелсингер (Patrick Gelsinger) показал кремниевую пластину с процессорами Arrow Lake, выполненными по техпроцессу 20A (20 ангстрем или 2 нм). Эти чипы появятся в 2024 году и станут первыми за 13 лет носителями новой архитектуры транзисторов. На мероприятии глава Intel раскрыл кое-какие детали будущих архитектур, что можно считать официальным подтверждением появившихся ранее утечек.

Источник изображения: Intel Значительным событием стало подтверждение планов Intel начать выпуск 2-нм процессоров в 2024 году — раньше, чем это сделают компании TSMC и Samsung, до этого показавшие значительный технологический отрыв от микропроцессорного гиганта. Компания Intel поставила перед собой цель освоить за четыре года выпуск процессоров на пяти новых технологических узлах и, похоже, строго следует этому плану. Более того, по ряду технологических новшеств Intel собирается оказаться впереди как Samsung, так и TSMC.

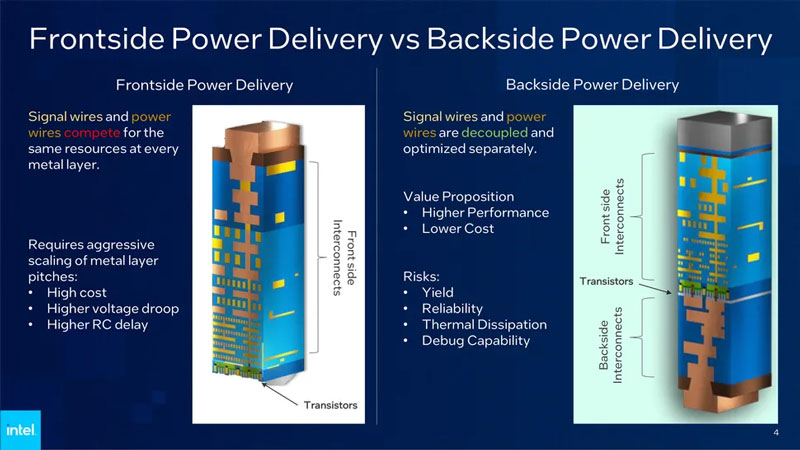

Пластина с чипами Arrow Lake В частности, компания Intel первой переведёт линии питания элементов процессоров на заднюю часть подложки. Сигнальные линии останутся на прежнем месте, а питание будет подаваться с обратной стороны непосредственно на транзисторы. Произойдёт это, начиная с транзисторов чипов Arrow Lake, которые компания уже выпускает в виде инженерных образцов. Разделение питания и сигнальных линий даст много преимуществ, хотя также будет сопряжено с технологическими трудностями. Разгрузка объёма пластины со стороны сигнального интерфейса позволит упростить разводку и повысить скорость работы сигнального интерфейса за счёт уменьшения длин соединений и, соответственно, снижения их сопротивления току. Такое же упрощение разводки питания (с обратной стороны) и даже увеличение сечения проводников питания позволит уменьшить переходные процессы и даже откроет путь к увеличению плотности размещения транзисторов. Компания TSMC, например, планирует внедрить похожую технологию не раньше 2026 года или на два года позже Intel.

Доставка питания сзади (справа на изображении). Слева — актуальный подход, когда сигнал и питание подаются в одном слое Но определённо революционным новшеством в процессорах Arrow Lake станут новые транзисторы RibbonFET Gate-All-Around (GAA) с каналами, полностью окружёнными затворами. Это будут первые с 2011 года новые транзисторы в процессорах Intel после начала производства транзисторов FinFET с вертикальными каналами (рёбрами), окружёнными затворами только с трёх сторон. Подобные транзисторы в собственной интерпретации (SF3E) уже выпускает компания Samsung, но она не готова сделать их массовыми. Компания Intel, похоже, готова организовать производство GAA-транзисторов на массовой основе. Архитектурно GAA-транзисторы Intel похожи на такие же транзисторы Samsung. Они точно также представлены расположенными друг над другом каналами в виде тонких нанолистов (наностраниц), окружённых затворами со всех сторон. В составе транзистора Intel использует четыре канала. По словам Intel, такая конструкция обеспечивает более быстрое переключение транзисторов при использовании управляющего тока аналогичного по силе току для FinFET. При этом GAA-транзистор занимает на подложке заметно меньше места, чем FinFET. Компания TSMC рассчитывает внедрить в производство собственную архитектуру GAA в 2025 году или на год позже Intel. В этом формально Samsung опередила своих конкурентов, но в плане массовости производства самых передовых решений она пока ничем похвастаться не может. |

|

✴ Входит в перечень общественных объединений и религиозных организаций, в отношении которых судом принято вступившее в законную силу решение о ликвидации или запрете деятельности по основаниям, предусмотренным Федеральным законом от 25.07.2002 № 114-ФЗ «О противодействии экстремистской деятельности»; |