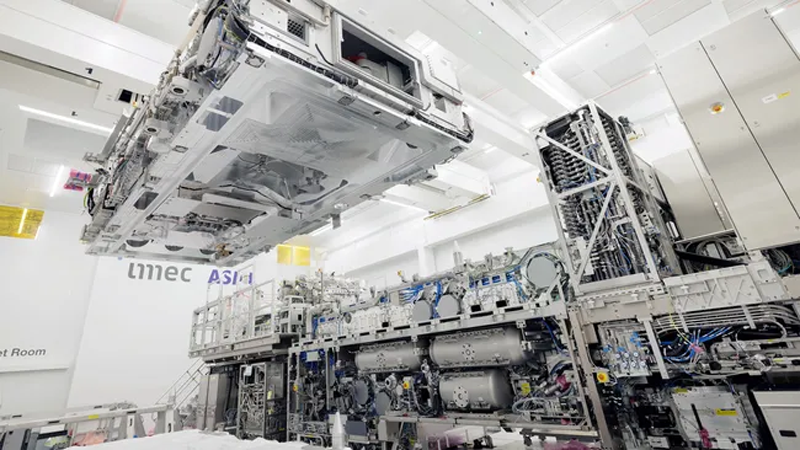

На днях бельгийский исследовательский центр Imec и компания ASML заключили пятилетнее соглашение, в рамках которого нидерландский производитель литографического оборудования предоставит Imec полный комплект самых современных инструментов для выпуска чипов и проверки качества продукции. Партнёрство позволит разработать и внедрить в промышленность техпроцессы с нормами менее 2 нм вплоть до атомарного уровня.

Источник изображения: Imec

Ранее исследователи Imec пользовались передовым литографическим оборудованием на родной площадке ASML в Вельдховене, Нидерланды. Подписанное соглашение позволит разместить аналогичное оборудование на площадке Imec, что облегчит и упростит работу сотрудникам центра и их партнёрам из академических и коммерческих кругов.

Новейшее оборудование от ASML, включая сканер EUV с высоким значением числовой апертуры (High-NA) стоимостью $350 млн, будет интегрировано в пилотную линию NanoIC по обработке кремниевых пластин в Бельгии. Ранее в линию NanoIC вложились ЕС и власти Фландрии. Собственно, поставка ASML во многом будет оплачена за счёт финансирования из европейских фондов и программ, направленных на разработку передовых полупроводниковых технологий.

Вместе со сканером Twinscan EXE (High-NA 0,55) в Imec будут доставлены сканер Twinscan NXE (NA 0,33), Twinscan NXT (DUV, 193 нм), оптические метрологические инструменты ASML YieldStar и одно- и многолучевые инспекционные инструменты HMI. Бельгийцы получат все лучшие «игрушки» ASML, а взамен передадут для внедрения в промышленность технологии литографического производства с технологическими нормами менее 2 нм и будут разрабатывать техпроцессы двух следующих десятилетий.

Отличным дополнением к совместной работе над технологическими узлами следующего поколения для логических микросхем с техпроцессом менее 2 нм, станет сотрудничество в области технологий производства DRAM, кремниевой фотоники и передовых решений для упаковки чипов — всего того, что крайне востребовано современной полупроводниковой промышленностью, явно подошедшей к технологическому барьеру классических техпроцессов.

Источник:

MWC 2018

MWC 2018 2018

2018 Computex

Computex

IFA 2018

IFA 2018

Подписаться

Подписаться