В ноябре 2000 года в продажу поступил новый процессор Pentium 4, который реализовал принципиально новую микроархитектуру x86 со времён Pentium Pro. До выхода P4 на рынке преобладало ядро P6, представленное процессорами Pentium II и Pentium III. За это время люди, обращавшие внимание на этот рынок, усвоили одну вещь: народ покупает мегагерцы. Intel учла этот факт и команда Willamette, работавшая в Санта-Кларе, руководствовалась именно гонкой мегагерц. Это можно увидеть как в рекламе Pentium 4, так и в технической литературе, где недавно были опубликованы детали разработки процессора. В нашей статье вы узнаете, что преемник наиболее успешной микроархитектуры x86 - это созданный с нуля процессор, работающий на запредельных частотах.

Мы рассмотрим возможные решения и варианты дизайна, взятые разработчиками при создании этого мегагерцового монстра. Особое внимание придется уделить инновациям, тому, как они вписываются в общую философию дизайна этого процессора и взаимодействуют с конечными приложениями. Мы рассмотрим сверх-длинный конвейер, структуру кэша с отслеживаниями (trace cache), арифметико-логическое устройство, работающее с удвоенной скоростью и другие аспекты процессора.

Лучше всего рассматривать данную статью, как статью о процессоре P4, где G4e используется лишь для сравнения и объяснения новых технологий. На примере G4е продемонстрировано как "стандартно" работает та или иная технология. Затем мы перейдем к отличиям ее реализации в P4.

Перед тем как детально рассматривать Pentium 4, полезно вспомнить основы дизайна процессоров.

Основной поток команд

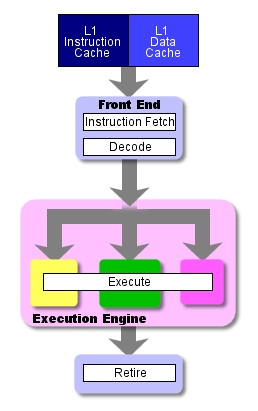

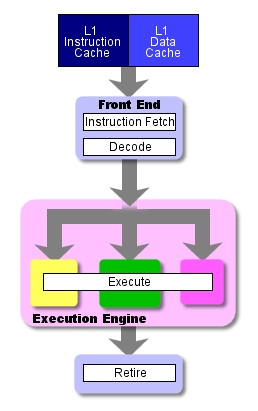

Когда разговор идёт о процессорах, основными понятиями считаются препроцессор (front end) и постпроцессор (back end, execution engine). Когда инструкции забираются из кэша или из оперативной памяти, их необходимо декодировать и отправить на выполнение. Эти три операции (получение инструкций, декодирование и отправка на выполнение) происходят на препроцессоре (front end).

Так выглядит основной поток команд в процессоре

Команды приходят из кэша на препроцессор и поступают затем на постпроцессор, где и выполняются. Как только команды будут обработаны постпроцессором, результат их выполнения попадает обратно в оперативную память. Процесс, когда команды ЗАБИРАЮТСЯ из кэша, ДЕКОДИРУЮТСЯ во внутреннюю форму, понятную процессору, ВЫПОЛНЯЮТСЯ и результат ЗАПИСЫВАЕТСЯ в оперативную память, и составляет основной четырёхступенчатый конвейер. Примерно этому учат на различных курсах в ВУЗах разработчиков процессоров. Каждую из этих ступеней команда должна проходить ровно за один такт. Ровно за один такт каждая ступень выполняет всю свою логику и пересылает команду на следующую ступень. Поэтому чем быстрее каждая из ступеней выполняет свои функции, тем быстрее работает весь процессор и тем выше его тактовая частота.

Четырёхступенчатая конвейерная обработка

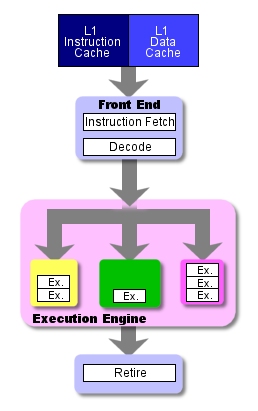

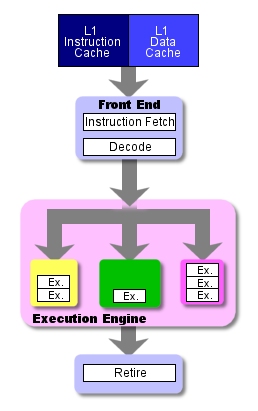

Эта схема представляет "стандартный" путь прохождения команд через процессор, и как мы только что заметили, на выполнение одной команды здесь требуется ровно один цикл. Большинство процессоров действительно выполняют команды за один цикл (в P4 даже существуют команды, выполняемые за половину цикла), но существуют сложные команды, которые проходят стадию ВЫПОЛНЕНИЯ за несколько циклов. Для согласования при выполнении таких сложных инструкций различные устройства задействуют свои собственные исполнительные конвейеры (некоторые - одноступенчатые, некоторые - многоступенчатые), так что они могут добавить ещё несколько ступеней к основному конвейеру процессора.

Четырёхступенчатая конвейерная обработка

с конвейерами на стадии ВЫПОЛНЕНИЯ

Поясним наши слова. Когда мы говорим о количестве ступеней в конвейере процессора, мы имеем в виду идеальный процессор, где каждая инструкция проходит ступень ВЫПОЛНЕНИЯ ровно за один такт, но большинство инструкций проходят несколько ступеней ВЫПОЛНЕНИЯ в различных функциональных устройствах.

Если Вы заметили ошибку — выделите ее мышью и нажмите CTRL+ENTER.

MWC 2018

MWC 2018 2018

2018 Computex

Computex

IFA 2018

IFA 2018